## GOVT. POLYTECHNIC SAMBALPUR RENGALI

# DEPARTMENT OF ELECTRONICS AND TELECOMMUNICATION ENGINEERING LECTURE NOTES

Year & Semester: 3<sup>RD</sup> Year, V Semester Subject Code/Name: TH-2, VLSI & EMBEDDED SYSTEM

## **UNIT-1 INTRODUCTION TO VLSI & MOS TRANSISTOR**

#### HISTORICAL PERSPECTIVE- INDRODUCTION-

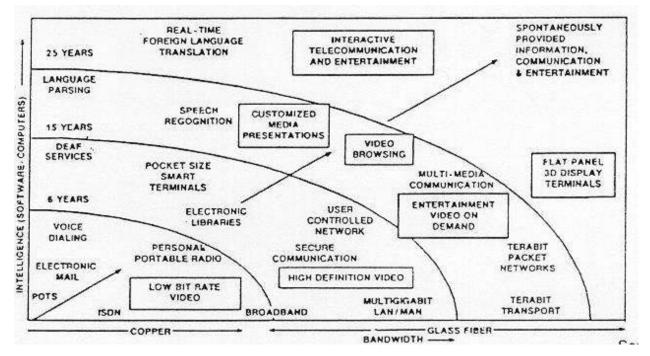

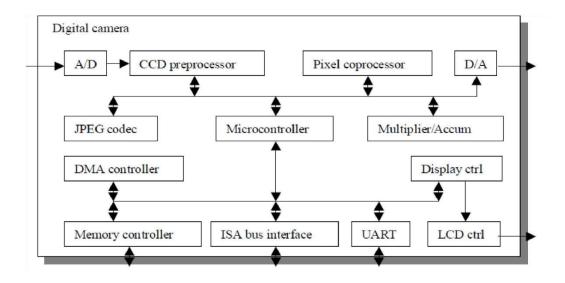

The electronics industry has achieved a phenomenal growth over the last two decades, mainly due to the rapid advances in integration technologies, large-scale systems design - in short, due to the advent of VLSI. The number of applications of integrated circuits in high-performance computing, telecommunications, and consumer electronics has been rising steadily, and at a very fast pace.

The current leading-edge technologies (such as low bit-rate video and cellular communications) already provide the end-users a certain amount of processing power and portability. This trend is expected to continue, with very important implications on VLSI and systems design.

One of the most important characteristics of information services is their increasing need for very high processing power and bandwidth (in order to handle real-time video, for example).

The other important characteristic is that the information services tend to become more and more personalized (as opposed to collective services such as broadcasting), which means that the devices must be more intelligent to answer individual demands, and at the same time they must be portable to allow more flexibility/mobility.

As more and more complex functions are required in various data processing and telecommunications devices, the need to integrate these functions in a small system/package is also increasing. The level of integration as measured by the number of logic gates in a monolithic chip has been steadily rising for almost three decades, mainly due to the rapid progress in processing technology and interconnect technology.

YEAR

COMPLEXITY (number of logic blocks per chip)

| Single transistor              |      | 1959         | les           | s than 1         |  |

|--------------------------------|------|--------------|---------------|------------------|--|

| Unit logic (one gate)          |      | 1960         | 1             |                  |  |

| Multi-function                 |      | 1962         | 2 -           | 4                |  |

| <b>Complex function</b>        |      | 1964         | 5 - 20        |                  |  |

| Medium Scale Integration (MSI) |      | 1967         | 20            | - 200            |  |

| Large Scale Integration (LSI)  |      | 1972         | 200 - 2000    | Very Large Scale |  |

| Integration (VLSI)             | 1978 | 2000 - 20000 | Ultra Large S | cale Integration |  |

| (ULSI) 1989                    |      | 20000 - ?    |               |                  |  |

The logic complexity per chip has been (and still is) increasing exponentially. The monolithic integration of a large number of functions on a single chip usually provides:

- Less area/volume and therefore, compactness

- Less power consumption

- Less testing requirements at system level

- Higher reliability, mainly due to improve on-chip interconnects

- Higher speed, due to significantly reduced interconnection length

Significant cost savings

#### INTRODUCTION TO MOS TRANSISTOR & BASIC OPERATION OF MOSFET-

- The MOSFET transistor is a semiconductor device is used for switching and amplifying signals in the electronic devices.

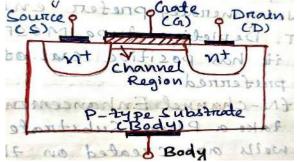

- The full form of MOSFET is Metal Oxide Semiconductor Field Effect Transistor. The MOSFET is a four terminal device with Source (S), Gate (G), Drain (D) and Body (B) terminals.

- The body of the MOSFET is frequently connected to the source terminal. So, making it a three terminal device.

- The MOSFET works by applying voltage at gate terminal, which is used to control the flow of current within the device.

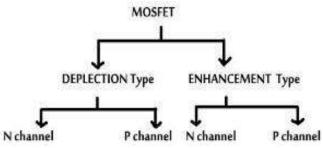

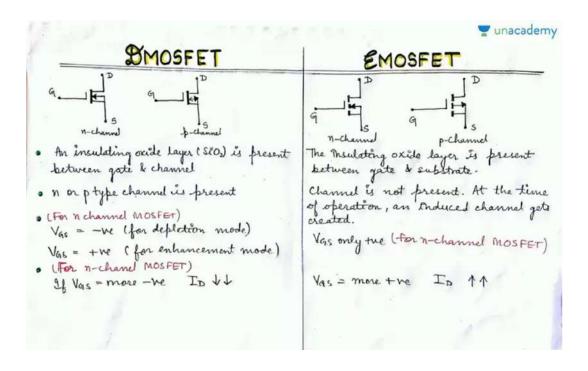

- Types of MOSFET-

• Enhancement type MOSFET- When there is no channel present at zero gate bias is known as enhancement type MOSFET.

#### MOSFET: N-Channel Enhancement Type

Enhancement Type

• Depletion type MOSFET- When there is a channel present in a MOSFET at zero gate bias is known as depletion type MOSFET.

**Depletion Type**

MOSFET: P-Channel Depletion Type

- We generally prefer enhancement type MOSFET. Depletion type MOSFET conducts at 0V and it has positive cut off gate voltage so less preferred.

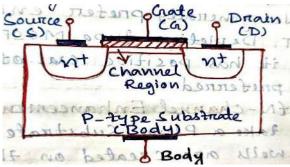

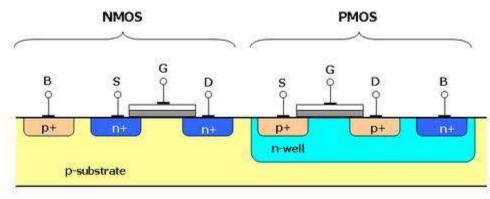

<u>NMOS-</u>

- First take a P-type substrate. After this two n-type wells are created on the p-type substrate. Out of two n wells one act as source and the other act as drain.

- The gate terminal formed between source and drain. A  $SiO_2$  layer is exist between gate terminal and substrate.

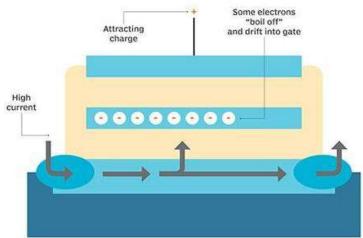

- Initially  $V_{GS}$  is kept 0V. Whenever we apply +ve voltage at the gate terminal, then the holes which are near this oxide layer will be pushed away and at the same time, the electrons will get attracted towards the gate terminal.

- As we keep increasing this voltage  $V_{GS}$  means gate voltage, then the holes will be pushed more and more deep in the substrate. The electrons will start accumulating near this oxide layer.

- The inversion layer of free electrons will get created near this oxide. This inversion layer will act as a channel between this drain and the source.

- If we apply the voltage between this drain and the source terminal, then the current can flow through this channel.

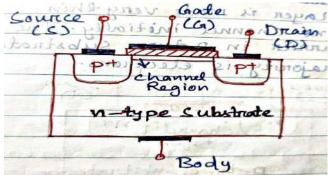

## PMOS-

- First take a n-type substrate. After this two p-type wells are created on the n-type substrate. Out of two p wells one act as source and the other act as drain.

- The gate terminal formed between source and drain. An oxide layer will be formed between gate terminal and substrate.

- In PMOS we apply -ve voltage at the gate terminal, because of that the electrons which are near this oxide layer will be pushed away and at the same time the holes will get attracted towards the gate terminal.

- As we keep increasing this voltageV<sub>GS</sub>, then the electrons will be pushed more and more deep in the substrate. The holes will start accumulating near this oxide layer.

- The inversion layer of holes will get created near this oxide. This inversion layer will act as a channel between this drain and source.

- If we apply the voltage between the drain and the source terminal, then current can flow through this channel.

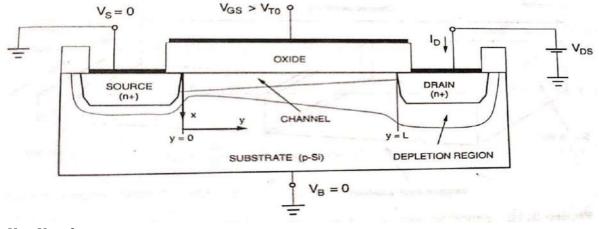

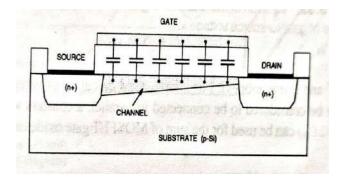

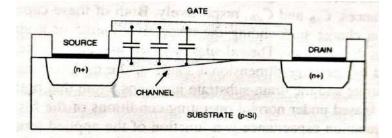

#### STRUCTURE AND OPERATION OF MOSFET (NMOS ENHANCEMENT TYPE)-

Structure-

- First take a P-type substrate. After this two n-type wells are created on the P-type substrate. Hence here two junctions formed between P and N type semiconductor. So, depletion layer formed at these junctions.

- Out of two n wells, one act as source and the other act as drain. The gate terminal formed between source and drain. A silicon oxide layer is present between gate terminal and substrate. So, there is no direct contact between gate and substrate.

- $SiO_2$  layer is very thin. This is known as gate oxide. Gate controls the movement of charge carrier near the surface of substrate. So, that the oxide layer is made very thin.

- There is no channel initially. The majority charge carrier in P-type substrate is holes and the majority is electrons.

Operation-

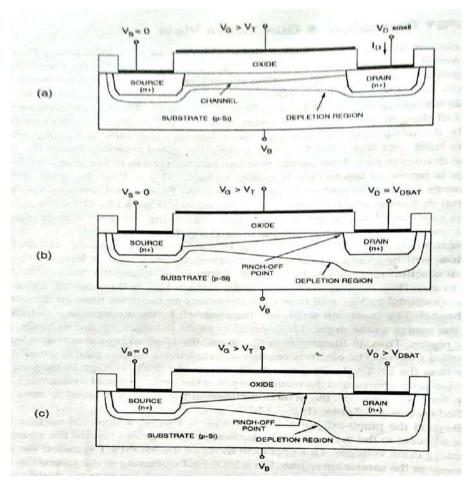

Initially  $V_{GS}$  is kept 0V. The substrate and the source terminals are connected together and they are connected to the ground terminal.

Assume that  $V_{ds} = 0$ .

- Whenever we apply the +ve voltage at this gate terminal, then the holes which are near this oxide layer will be pushed away from this gate and at the same time, the electrons get attracted towards this gate terminal.

- As we keep on increasing this voltage V<sub>gs</sub>, then the holes will be pushed more and more deeper in the substrate and the electrons will be accumulated near the substrate surface of gate terminal.

- The inversion layer of free electrons will get created near the oxide. This inversion layer will act as a channel between this drain and source.

- If we apply the voltage between this drain and source terminal, then the current can flow through this channel.

- The value of the V<sub>gs</sub> at which this inversion layer is created is known as the threshold voltage. Below this threshold voltage, there will not be any flow of current through the MOSFET.

- Whenever the V<sub>gs</sub>is greater than this threshold voltage, then the width of the channel is increases. Along with this channel, there will also be a depletion layer around this channel. When we apply the voltage V<sub>ds</sub>, then through the channel electrons get attracted towards this positive terminal and in this way, the current will establish in this way, the current will establish in this circuit.

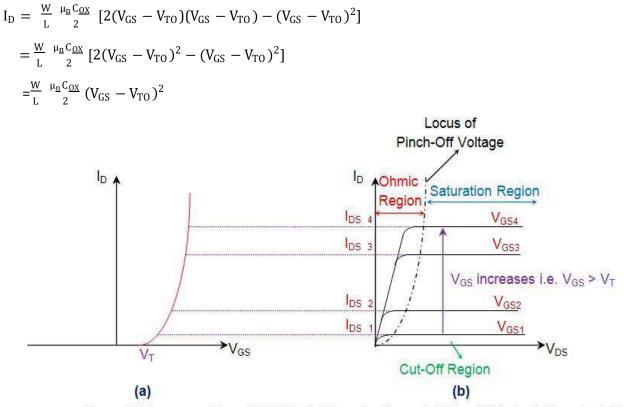

- As we keep on increasing  $V_{ds}$ , then at one particular voltage, the pinch off condition will occur. At that particular voltage, the drain current which is flowing through the circuit will get saturated.

- The voltage  $V_{ds}$ , at which this pinch off condition occurs is known as the saturation voltage and this saturation voltage can be expressed as  $V_{gs} V_t$ .

- For the fixed value of  $V_{gs}$ , if we further increase the value of  $V_{ds}$  the voltage difference between the gate and drain terminal will be even lesser than this threshold voltage and due to that, the channel will not get formed towards the drain terminal. So, it appears that the current through the channel should become zero.

- But actually still the current will flow through this channel and this current  $I_d$  will get saturated. Because the electrons which are passing through this channel can still be able to cross this depletion layer due to the electric force.

- Even if we increase the drain voltage, the current through this circuit will remain almost constant.

a) Operating in the linear region, b) operating at the edge of saturation and c) operating beyond saturation

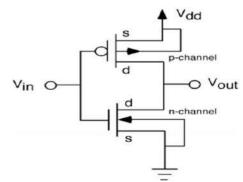

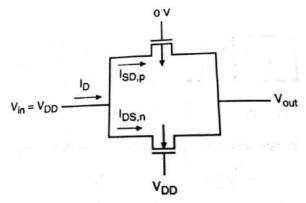

#### CMOS-

• CMOS stands for Complementary Metal Oxide Semiconductor. CMOS transistor consists of PMOS and NMOS. NMOS consists of N-type source and drain on a P type substrate. When a high voltage is applied to the gate, the NMOS will conduct and when a low voltage is applied to the gate, NMOS will not conduct.

- PMOS consists of P-type source and drain on an N-type substrate. When a high voltage is applied to the gate, the PMOS will not conduct. When a low voltage is applied to the gate, the PMOS will conduct.

- CMOS use same signal which turns on a transistor of one type and turn off a transistor of the other type.

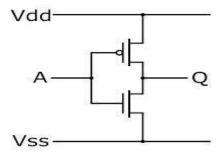

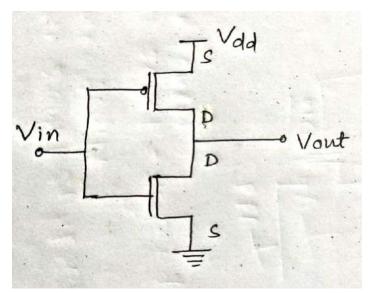

- Lets see a simple CMOS inverter.

- In CMOS inverter PMOS is connected to  $V_{DD}$  and the NMOS is connected to ground. The gate terminals of both NMOS and PMOS are connected together and act as the input terminal.

- The drains of both are connected together and act as the output terminal. The inverter has only two states. For a high input, the output is low and for a low input, the output is high.

- There is never a short circuit between  $V_{DD}$  and ground because in either state only one MOS transistor is conducting while the other is off.

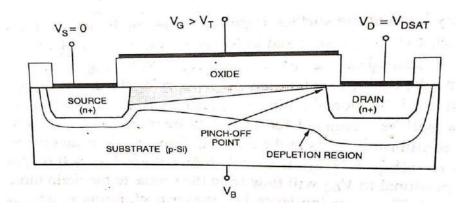

MOSFET V-I CHARACTERISTICS-

Gradual Channel Approximation-

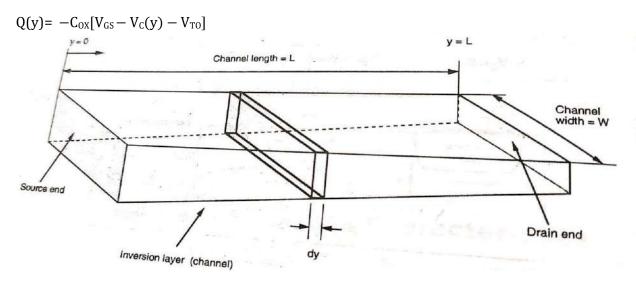

- We use the gradual channel approximation for establishing the MOSFET current voltage relationship.

- ▶ Using this method we find out the drain current I<sub>D</sub> in linear region and saturation region.

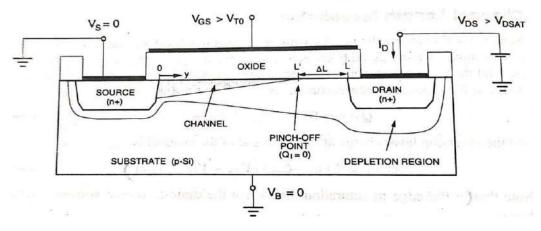

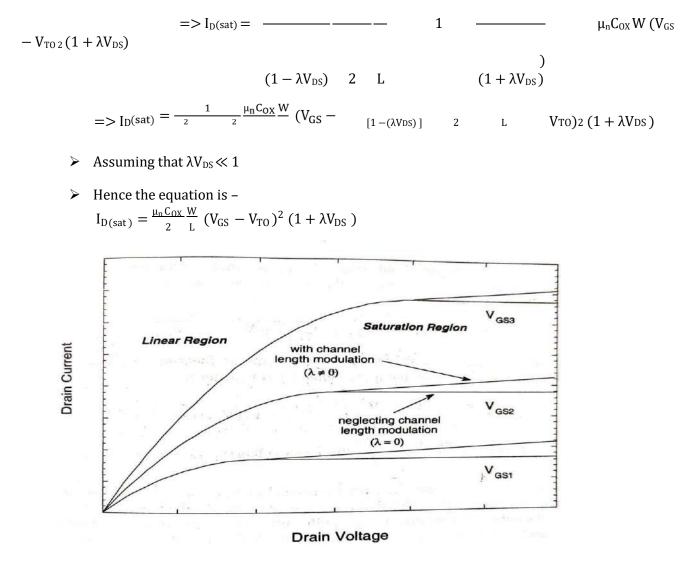

- When gradually V<sub>DS</sub> increases than V<sub>DSAT</sub> the channel length in MOSFET starts to decease. So another method named channel length modulation is used to find out the drain current with this new channel length.

- > Consider the cross sectional view of the n-channel MOSFET operating in linear mode.

- ▶ VGS > Vто

- Assume the coordinate system such that x –direction is perpendicular to the surface and the ydirection is parallel to the surface.

- > Assume that electric field component in y-direction is dominant compared to x direction.

- > The channel voltage is denoted by  $V_{C}(y)$ .

- ▶ At y=0, the  $V_C(y = 0) = V_S = 0$ .

- At y=L, the  $V_C(y = L) = V_{DS}$ .

- ▶ Let Q(y) is the mobile electron charge in channel-

Net voltage is

$Y=0, V=V_{GS}-V_{TO}$

$$Y=L, V=V_{GS}-V_{DS}-V_{TG}$$

Calculate the incremental resistance dR

$dR = -\frac{dY}{W\mu_n Q(y)}$

The above equation derived from a Basic resistance formula is-

${}_{\text{ID}}\,dVc = $$$$ ID $dR = -w\__{\mu n}Q(y)$ dy$$

$=> I_D dy = -W\mu_n q(y)dV_c$

Then integrate the both side

$$= > \int_{0} I_{D} dy = - \int_{0} W \mu_{n} Q(y) dV_{C}$$

$$= > I_{D}[L - 0] = -W \mu_{n} \int_{0}^{V_{DS}} Q(y) dV_{C}$$

$$= > I_{D}L = -W \mu_{n} \int_{0}^{V_{DS}} C_{OX}(V_{GS} - V_{C}(y) - V_{TO}) dV_{C}$$

$$= > I_{D}L = W \mu_{n} C_{OX} \int_{0}^{V} (V_{GS} - V_{C}(y) - V_{TO}) dV_{C}$$

$$= > I_{D} = \frac{1}{L} \frac{n \cdot OX}{2} [2(V_{GS} - V_{TO})V_{DS} - W_{UC} - V_{DS2}]$$

If we take  $\mu_{n}C_{OX} = K'$

$$K' \cdot W = K$$

$$Again if we take K'W = K L$$

$$- K = 2]$$

Then ID = 2 [2(V\_{GS} - V\_{TO})V\_{DS} - V\_{DS}]

> But when  $V_{DS} = V_{DSAT}$ ,

۶

$$V_{DS} = V_{GS} - V_{TO}$$

After substituting the value of  $V_{\mbox{\tiny DS}}$  in drain current equation, we get

n-Channel Enhancement type MOSFET (a) Transfer Characteristics (b) Output Characteristics

#### **Channel Length Modulation-**

- > Channel Length Modulation happens in saturation region.

- Channel length will change with respect to drain voltage of MOSFET.

- Charge density in channel is given by

$Q(y) = -C_{OX}(V_{GS} - V_C(y) - V_{TO})$

Inversion layer charge at source y=0 end is given by-

$$Q(y=0) = -C_{OX}(V_{GS} - V_{TO})$$

Inversion layer charge at drain end y=L is given by-

$$Q(y) = -C_{OX}(V_{GS} - V_{DS} - V_{TO})$$

> At the edge of saturation  $V_{DS} = V_{DSAT}$

$V_{DS} = V_{DSAT} = V_{GS} - V_{TO}$

Inversion layer charge at drain end (y=L) in saturation region is given by-

Q(y=L)=0

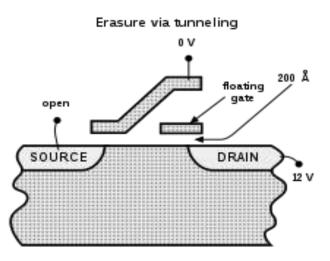

- If we further increase drain voltage beyond this saturation voltage then length of channel will decrease to L'.

- > Effective channel length in saturation region will become

$$L' = L - \Delta L$$

> At pinch off point of channel, channel voltage will beV<sub>DSAT</sub>.

$\begin{array}{c} \succ \quad \text{The} \quad \underbrace{-\frac{W}{2} \quad W_{GS}}_{\mu_{L}^{'}}(V_{GS}) & \text{drain current equation in saturation region with change in channel length is given by-} \quad I_{D(sat)} = \mu^{nCOX} - V_{TO})^2 \end{array}$

$$=>$$

ID(sat) 2 (L- $\Delta$ L) (VGS - VTO)<sup>2</sup>

$$=> I_{D(sat)} = \frac{1}{(1-\frac{\Delta L}{2})} - \frac{n \text{ ox}}{L} (V_{GS} - 1 \mu C W)^{2}$$

Here  $\Delta L \alpha \sqrt{V_{DS} - V_{DSAT}}$

> To simplify this drain current equation we will take-

$$\frac{\Delta L}{1 - \frac{1}{L}} = 1 - \lambda V_{DS}$$

#### $\lambda$ = Channel length modulation coefficient

So, drain current is given by

```

I_{D(sat)} = (\underline{\qquad} 1 - \lambda I V_{DS}) \mu n C_{20X} WL (V_{GS} - V_{TO})_2

```

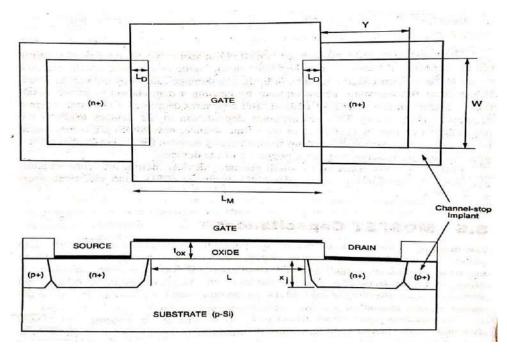

#### **MOSFET CAPACITANCES-**

The on chip capacitances found in MOS circuits are known as parasitic capacitance. These are unavoidable and unwanted capacitances exists in MOSFET due to its layout geometries and the manufacturing processes.

Most of these capacitances are distributed. Let's take the cross sectional and top view of MOSFET.

The overlap areas in both source and drain side denoted as  $L_D$ , they are symmetrical. Both source and drain diffusion regions have a width of W. the diffusion region length is denoted by 'y'.

The both source and drain diffusion region are surrounded by a P doped region, also called the channel stop implant. This channel stop implant. This channel stop implant region provides the electrical isolation from neighboring devices.

The total length of gate means the mask length is indicated by  $L_M$  and the actual length of the channel is denoted by L.

$L = L_M - 2. L_D$

Based on their physical origins, the parasitic device capacitances can be classified into two types-

- 2) Oxide related capacitance

- 3) Junction related capacitance

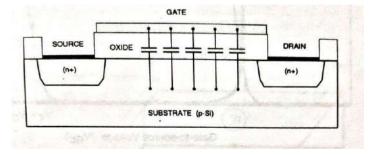

#### Oxide related capacitance-

A MOS transistor consists of a gate conductor and a semiconductor (substrate) separated by a gate dielectric.

So, it act as a parallel plate capacitance. Hence the gate oxide capacitance per unit area is given by-

```

c_{ox}

Cox= tox

Where c_{ox} = c_o c_r

```

Hence  $Cox = \epsilon t_{0} ox \epsilon_{r}$

```

\epsilon_{o}= 8.85x10<sup>-12</sup>Fm<sup>-1</sup> \epsilon_{r}= 3.9

```

The two overlap capacitances that arise as a result of this structural arrangement are called CGS(overlap) andCGD(overlap).

```

CGS(overlap) = Cox W LD

CGD(overlap) = Cox W LD

```

The channel region is connected to the source, drain and substrate. Depending on biasing condition the MOSFET operates in 3 regions i.e, cut off, linear and saturation.

#### **Cut-off Mode-**

In this mode there is no channel formed because of that there is no connection present between source and drain. Therefore gate to source and gate to drain capacitances are both equal to zero.

$C_{gs} = C_{gd} = 0$

So, the total capacitance is-

$C_{gs}(total) = C_{gs} + C_{GS}(overlap) = 0 + C_{ox}.W.L_D = C_{ox}.W.L_D$

$C_{gd}(total) = C_{gd} + C_{GD}(overlap) = 0 + C_{ox}.W.L_D = C_{ox}.W.L_D$

Due to absence of channel there is a direct contact between gate and body.

So,  $C_{gb} = C_{ox}.W.L$

#### Linear Mode-

In this mode there is channel present between source and drain. This inversion layer on the surface cover the substrate and there is no connection between substrate and gate. Thus  $C_{gb} = 0$ .

$C_{gb} = C_{gb(total)} = 0$

$C_{gs}$  and  $C_{gb}$  both are gate to channel capacitance between the source and drain. Hence  $C_{gs} \cong C_{gd} \cong 1$ 2–Cox.W.L

So,

$$Cgs(total) = Cgs + CGS(overlap) = {}_{2-}CoxWL + CoxWLD$$

$$1$$

$$Cgd(total) = Cgd + CGD(overlap) = {}_{-}CoxWL + CoxWLD$$

$$2$$

#### Saturation Mode-

In this mode the inversion layer on the surface does not extend to the drain means it is pinched off.

So,

$$C_{gd} = 0$$

$C_{gd(total)} = C_{gd} + C_{GD(overlap)} = C_{ox}.W.L_D$

Since the source is still connected to the conducting channel. So, the  $C_{gb} = 0$ .

$$C_{gb} = C_{gb}(total) = 0$$

As the channel is present near the source only. So, this part approximated as two-third part of the channel.

So,

$$C_{gs} \cong \frac{2}{3} C_{ox} \cdot W$$

. L

$$C_{gs(total)} = C_{gs} + C_{GS(overlap)} = -\frac{2}{C_{ox}} W \cdot L + C_{ox} \cdot W \cdot L_D$$

3

#### JUNCTION CAPACITANCE-

Whenever we have a PN junction whether or not we apply any voltage across the junction, we always get a depletion region across the junction.

Because of that the n region and P region act as two plates and the depletion region act as dielectric. So, this is the capacitance of the PN junction.

$C_{sb}$  and  $C_{db}$  are function of  $V_{sb}$  and  $V_{db}$  because it modulating the depth of the junction.

Capacitance depends on the depth of the junction, as junction depth increases further and further, as we give reverse bias.

All of these surfaces contribute to the source to body capacitance. The height of the region is 'h', the area of the source is ' $A_s$ ', area of the drain is ' $A_D$ ', the perimeter of the drain is ' $P_D$ ' and the perimeter of the source is ' $P_s$ '.

The area of the junction for the source side is-  $A_s + P_s h$

The area of the junction for the drain side is-  $A_D + P_D h$

Junction capacitance of source is  $C_{js} = (\underline{A^{s+}}d^{P_{j}sh})\epsilon_{si}$

Junction capacitance of drain is  $C_{js} = (\underline{\qquad}^{AD}d^{+P_jDh})\epsilon_{si}$

Where  $d_j$  = depth of the junction

$\epsilon_{si}$ = Permitivity of the junction

### MODELLING OF MOS TRANSISTORS INCLUDING BASIC CONCEPT OF THE SPICE LEVEL MODEL-

- Modeling of MOS device consist of writing a set of equations that link voltages and currents, in order to simulate and predict the behavior of a single device and hence the complete circuit.

- Main aim of the model is to evaluate the current I<sub>p</sub> which flows between drain and source, depending on the supply voltages V<sub>D</sub>, V<sub>G</sub>, V<sub>S</sub> &V<sub>B</sub>.

- The most popular circuit simulator is SPICE (simulation program with IC emphasis).

- SPICE describes the device with a set of equations that represent the equivalent circuit.

- The basic drain current models are level-1, level-2 & level-3.

Level-1 model equations:-

- 1. it is the simplest I-V description of MOS which is basically the GCA based model originally concerned by Sah in early 1960s and later developed by shichman and Hodges.

- 2. The equation used in level1 n-channel MOS model in SPICE are  $I_D$  (Linear) $\mu_n$ Cox w/L[2(V<sub>GS</sub> – V<sub>ih</sub>)V<sub>DS</sub> –V<sup>2</sup><sub>DS</sub>][1+ $\lambda$  V<sub>DS</sub>]

For  $V_{GS} \ge V_{TH} \& V_{DS} < V_{GS} - V_{TH}$ .  $I_D$  (saturation) =  $\mu C_{ox} w / 2L (V_{GS} - V_{th})^2 (1 + \lambda V_{DS})$ For  $V_{GS} \ge V_{th} \& V_{DS} \ge V_{gs} - V_{th}$

Where, L is the effective length i.e.,  $L=L_M-2L_D$

Where  $L_m$ =total length of gate oxide

$L_D$ = length of source & drain extended bel oxide & (1+ $\lambda V_{DS}$ ) is the empirical channel length modulation which is sorting of the length of the inverted channel region with increase in drain voltage. It increases the drain current.

&  $\lambda$ = channel length modulation parameter.

□ Thus, level-1 model offers a useful estimate of the circuit performance without using a large no. of device model parameter.

## Level-2 model equations:-

- To obtain a more accurate model for drain current, it is necessary to eliminate some of the simplifying assumption in GCA analysis.

- Considering depletion charge and its dependence on channel voltage, the drain current-

$\mu CoxW = \frac{3}{2}$

$I_{D} = \{ (V_{GS} - V_{FB} - (2\emptyset F) - V_{DS}/2) V_{DS} - 2/3Y [V_{DS} - V_{BS} + | 2\varphi F | (1 - \lambda VDS)L \} \}$

Where, V<sub>FB</sub>=Flat band voltage (ie; flat energy band in the semiconductor when a voltage is applied at gate).

$\phi_F$ =Fermi potential describes the carrier concentration in the semiconductor.

$V_{BS}$ =Substrate to Source Voltage .

Y=Substrate bias coefficient.

- The saturation is reached when the channel charge at the drain end is Zero.

- The saturation voltage:-

$V_{DSAT}=V_{GS}-V_{FB} - |2\phi_F| + Y^2[1 - \sqrt{1 - 2/Y^2(V_{GS} - V_{FB})}] \&$ saturation mode current is :- $I_D=I_{DSAT} 1/1 - \lambda V_{DS}$ Where  $I_{DSAT}$  is saturated using  $V_{DS}=V_{DSAT}$ .

- Level 2 model generates more accurate results than Level 1,but its accuracy is still not sufficient to achieve good experimental data for short & narrow channel MOS. <u>Level 3 model equations:-</u>

- Level 3 has been developed. for simulation of short channel MOS.

- It can represent the characteristics of MOS for channel length 2mm.

- The I-V equation are calculated same as Lavel2.

- However the Current equation in linear region has been simplified using Taylor Series expansion which is more approx then level 2 model.

- Lavel 3 model equation are mainly empirical bios it imprones the accuracy of model & limit the complexity of calculation and also the amount of required simulation time.

- The drain current in linear region is:-

$I_D=\mu_S C_O X W/L(V_{GS}-V_{TH}-1+FB/2 VDS)V_{DS}$ , Where,  $F_B=YFS/4\sqrt{|2\phi f| + V_{SB}}+F_n$ Where  $F_B$  express the dependence of depletion charge on the 3-D geometry of MOS.  $F_s$  =specifies short channel effect;  $F_n$ =Specifics narrow width effect  $M_s$ =Surface mobility =  $\mu/1+\theta(V_{GS}-V_{th})$

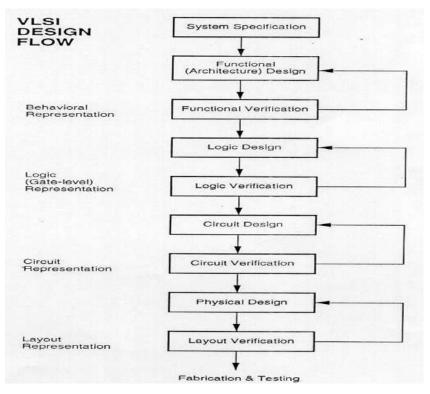

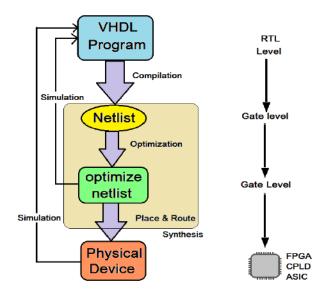

#### **VLSI DESIGN FLOW-**

The VLSI design flow starts with a formal specification of a VLSI chip, follows a series of steps and eventually produced a packaged chip.

1) System specification-

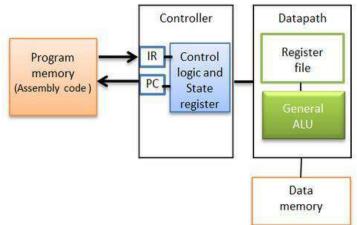

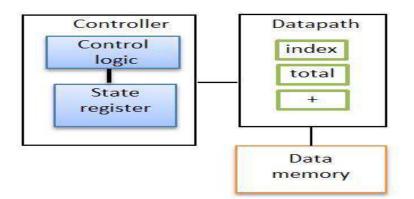

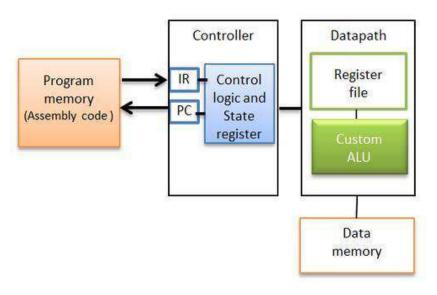

It is a high level representation of the system. The factors to be considered in this process include: performance, functionality, size, speed and power. The specification of a system is a compromise between market requirements, technology and economic viability. 2) Functional design-

With the help of specification, design engineers decide the architecture. This includes decisions like type of processor, no. of ALUs, floating point units, number and structure of pipelines etc.

In this step these functional units of the system are identified and also identifies the interconnect requirements between the units. It is a Resistor Transfer Level(RTL) description is done using Hardware Description Language (HDL) such as VHDL or Verilog.

3) Functional verification-

In this step the functional design is tested to verify its correctness.

4) Logic design-

The functional design can be refined into logic level design using gates, flip-flop etc. The RTL design is decomposed into gate level netlist.

5) Logic verification-

In this step the logic design of the system is simulated and tested to verify its correctness.

6) Circuit design-

The purpose of circuit design is to develop a circuit representation based on the logic design. This is the transistor level design. The every logic design realized into typical CMOS transistors. Then define the interconnection between the transistors.

7) Circuit verification-

Circuit verification is used to verify the correctness of each components.

8) Physical design-

In this step the circuit representation is converted into a geometric representation. The geometric representation of a circuit is called a layout.

9) Layout verification-

In this step various verification and validation checks are performed on the layout. 10) Fabrication and testing-

After layout verification, the design is ready for fabrication. Then the entire layout is fabricated on wafer. Each chip is then packaged and tested to ensure that it meets all the design specification and function properly.

#### Y CHART-

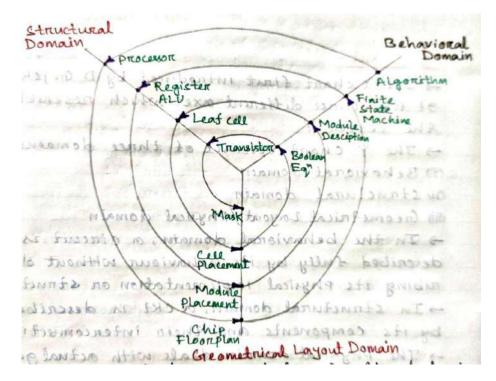

The Y-chart consists of three major domains, namely:

- behavioral domain

- structural domain

- Geometrical layout domain

- The design flow starts from the algorithm that describes the behavior of the target chip. The corresponding architecture of the processor is first defined.

- > It is mapped onto the chip surface by floor planning.

- The next design evolution in the behavioral domain defines finite state machines (FSMs) which are structurally implemented with functional modules such as registers and arithmetic logic units (ALUs).

- These modules are then geometrically placed onto the chip surface using CAD tools for automatic module placement followed by routing, with a goal of minimizing the interconnects area and signal delays.

- > The third evolution starts with a behavioral module description. Individual modules are then implemented with leaf cells.

- At this stage the chip is described in terms of logic gates (leaf cells), which can be placed and interconnected by using a cell placement & routing program.

- The last evolution involves a detailed Boolean description of leaf cells followed by a transistor level implementation of leaf cells and mask generation.

- In standard-cell based design, leaf cells are already pre-designed and stored in a library for logic design use.

DESIGN HIERARCHY-

- The use of hierarchy, or "divide and conquer" technique involves dividing a module into submodules and then repeating this operation on the sub-modules until the complexity of the smaller parts becomes manageable.

- This approach is very similar to the software case where large programs are split into smaller and smaller sections until simple subroutines, with well-defined functions and interfaces, can be written.

- In the above diagram The adder can be decomposed progressively into one- bit adders, separate carry and sum circuits, and finally, into individual logic gates. At this lower level of the hierarchy, the design of a simple circuit realizing a well-defined Boolean function is much easier to handle than at the higher levels of the hierarchy.

- In the physical domain, partitioning a complex system into its various functional blocks will provide a valuable guidance for the actual realization of these blocks on chip.

#### **VLSI DESIGN STYLES-**

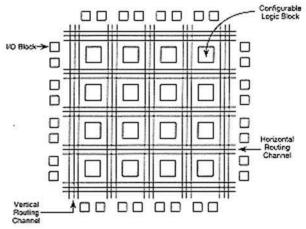

#### Field Programmable Gate Array (FPGA)

- Fully fabricated FPGA chips containing thousands of logic gates or even more, with programmable interconnects, are available to users for their custom hardware programming to realize desired functionality.

- > This design style provides a means for fast prototyping and also for cost-effective chip design, especially for low-volume applications.

- A typical field programmable gate array (FPGA) chip consists of I/O buffers, an array of configurable logic blocks (CLBs), and programmable interconnect structures. The programming of the interconnects is implemented by programming of RAM cells whose output terminals are connected to the gates of MOS pass transistors.

- The CLB is configured such that many different logic functions can be realized by programming its array.

- The typical design flow of an FPGA chip starts with the behavioral description of its functionality, using a hardware description language such as VHDL. The synthesized architecture is then technology-mapped (or partitioned) into circuits or logic cells.

- > At this stage, the chip design is completely described in terms of available logic cells. Next, the placement and routing step assigns individual logic cells to FPGA sites (CLBs) and determines the routing patterns among the cells in accordance with the netlist.

- After routing is completed\_performance of the design can be simulated and verified before downloading the design for programming of the FPGA chip. The programming of the chip remains valid as long as the chip is powered-on, or until new programming is done. In most cases, full utilization of the FPGA chip area is not possible - many cell sites may remain unused.

#### **Gate Array Design**

- In view of the fast prototyping capability, the gate array (GA) comes after the FPGA. While the design implementation of the FPGA chip is done with user programming, that of the gate array is done with metal mask design and processing.

- ➤ Gate array implementation requires a two-step manufacturing process: The first phase, which is based on generic (standard) masks, results in an array of uncommitted transistors on each GA chip.

- ➤ In the second phase these uncommitted chips can be stored for later customization, which is completed by defining the metal interconnects between the transistors of the array.

- Since the patterning of metallic interconnects is done at the end of the chip fabrication, the turnaround time can be still short, a few days to a few weeks.

#### Standard-Cells Based Design

- > The standard-cells based design is one of the most prevalent full custom design styles which require development of a full custom mask set. The standard cell is also called the poly cell.

- In this design style, all of the commonly used logic cells are developed, characterized, and stored in a standard cell library. A typical library may contain a few hundred cells including inverters, NAND gates, NOR gates, complex AOI, OAI gates, D-latches, and flip-flops.

- Each gate type can have multiple implementations to provide adequate driving capability for different fan outs. For instance, the inverter gate can have standard size transistors, double size

transistors, and quadruple size transistors so that the chip designer can choose the proper size to achieve high circuit speed and layout density.

To enable automated placement of the cells and routing of inter-cell connections, each cell layout is designed with a fixed height, so that a number of cells can be abutted side-by-side to form rows. The power and ground rails typically run parallel to the upper and lower boundaries of the cell, thus, neighboring cells share a common power and ground bus.

#### **Full Custom Design**

- Although the standard-cells based design is often called full custom design, in a strict sense, it is somewhat less than fully custom since the cells are pre-designed for general use and the same cells are utilized in many different chip designs.

- In a full custom design, the entire mask design is done anew without use of any library. However, the development cost of such a design style is becoming prohibitively high. Thus, the concept of design reuse is becoming popular in order to reduce design cycle time and development cost.

- The most rigorous full custom design can be the design of a memory cell, be it static or dynamic. Since the same layout design is replicated, there would not be any alternative to high density memory chip design.

- For logic chip design, a good compromise can be achieved by using a combination of different design styles on the same chip, such as standard cells, data-path cells and PLAs. In real full-custom layout in which the geometry, orientation and placement of every transistor is done individually by the designer, design productivity is usually very low - typically 10 to 20 transistors per day, per designer.

- In digital CMOS VLSI, full-custom design is rarely used due to the high labor cost. Exceptions to this include the design of high-volume products such as memory chips, high- performance microprocessors and FPGA masters.

#### **Semi-Custom Design**

Semicustom technique is used for the design of <u>integrated circuits</u> that is based on the use of fully characterized libraries of circuit elements produced by the manufacturer of the device. The designer is therefore not concerned with low-level details of semiconductor material electrical properties, and can instead concentrate on the functional behaviour of the design. Most <u>ASIC</u> circuit designs (for instance <u>gate arrays</u>) are produced by this method.

#### COMPARISION BETWEEN FULL CUSTOM AND SEMI-CUSTOM DESIGN IN VLSI.

| FULL CUSTOM DESIGN                                                                                                                                       | SEMI CUSTOM DESIGN                                                                               |

|----------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|

| All mask layers are customised in full<br>custom design                                                                                                  | It uses pre-designed logic cell(and gates,<br>OR gate, multiplexers) known as standard<br>cells. |

| In full custom design, all logic cells, circuits<br>or layouts are designed specifically. Design<br>doesn't use pretested or pre-characterized<br>cells. | Designer used pre-tested or pre-<br>characterized cell.                                          |

| This approach is considered only when there is no suitable existing                                                                                      | Widely used                                                                                      |

| Offers high performance lower cost as<br>compared to semi.                                                                                               | More cost. Low performance.                                                                      |

| Design time and complexity is more.                                                                                                                      | Design time and complexity is less                                                               |

| Eg: Microprocessor                                                                                                                                       | Eg. Digital logics                                                                               |

Difference between enhancement and depletion type nMOS transistor.

## <u>UNIT -2</u>

## **FABRICATION OF MOSFET**

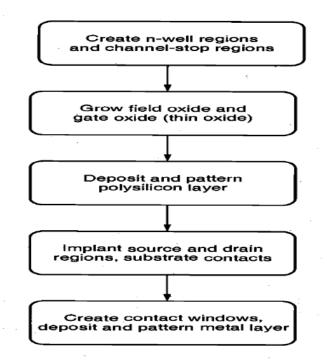

## SIMPLIFIED PROCESS SEQUENCE FOR FABRICATION-

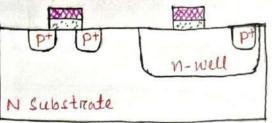

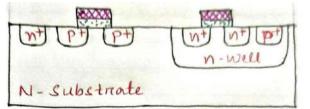

- CMOS fabrication technology requires both NMOS and PMOS transistor to be built on the same chip substrate.

- To accommodate both NMOS & PMOS devices, special regions must be created in which the semiconductor type is opposite to the substrate type. These special regions are called wells or tubs.

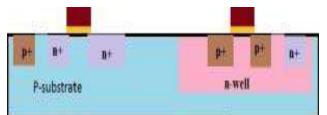

- So, a n well is formed in a P substrate and a P well is formed in a n substrate. The simplified process sequence for the fabrication of CMOS-

- The process starts with the creation of the n well regions for PMOS and p well regions for NMOS by ion implantation into the substrate.

- Ion implantation is the process of adding impurities to a silicon wafer.

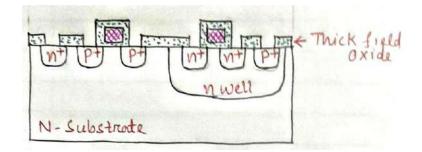

- Then a thick oxide is grown in the regions surrounding the NMOS and PMOS active regions. The thin gate oxide is subsequently grown on the surface through thermal oxidation.

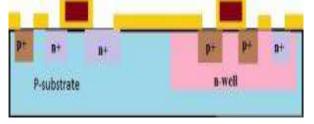

- Again a polysilicon layer is deposited on the surface of the oxide layers and selectively removed to form the gate.

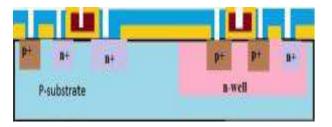

- These steps are followed by the creation of n+ and P+ regions.

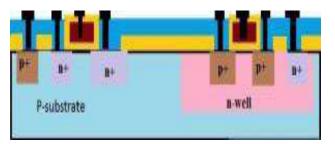

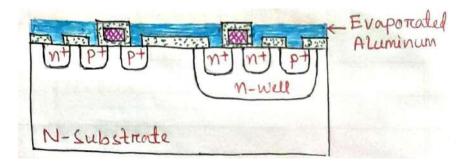

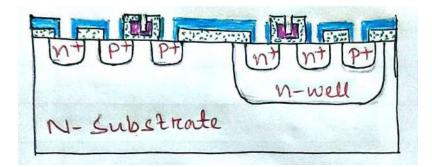

- At last metallization is done means creation of metal interconnects.

- Metallization is the process by which the components of IC's are interconnected by aluminum conductor.

- Channel stop implant is used to prevent the formation of any unwanted channels between two neighboring regions. Hence channel stop implants act to electrically isolate neighboring devices built on the same substrate.

## **BASIC STEPS OF FABRICATION-**

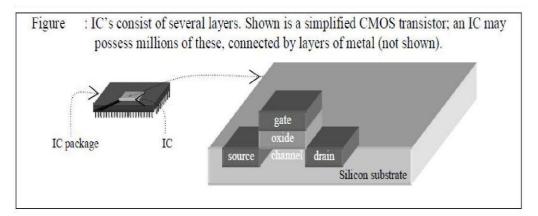

- The fabrication cycle of VLSI chips consists of a sequential set of basic steps which are wafer preparation, oxidation, lithography and etching.

- During fabrication process, the devices are created on the chip. So, IC may be viewed as a set of patterned layers.

- A layer must be patterned before the next layer of material is applied on the chip.

- Pattering uses the process of lithography. The process used to transfer a pattern to a layer on the chip is called lithography.

- The lithography sequence must be repeated for every layer.

Steps:

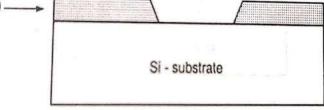

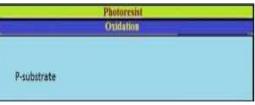

First we take a Si substrate.

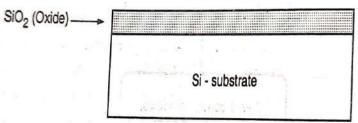

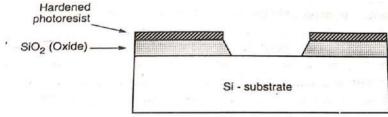

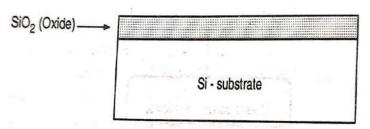

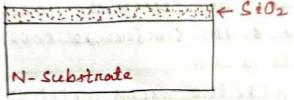

The sequence starts with the thermal oxidation of the silicon surface. Due to which oxide layer formed of 1mm thickness.

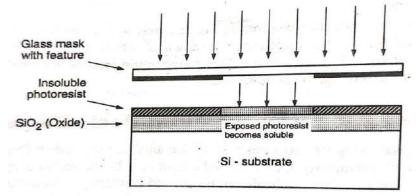

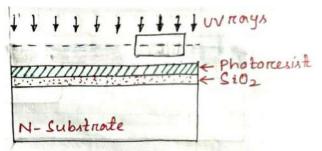

> The entire oxide surface is then covered with a layer of photoresist.

| Photoresist              | -         |             |                                                                                                                 |  |

|--------------------------|-----------|-------------|-----------------------------------------------------------------------------------------------------------------|--|

| SiO <sub>2</sub> (Oxide) |           |             |                                                                                                                 |  |

|                          | general a | 1971        | 3                                                                                                               |  |

|                          | 1 10 10   | Si - sub    | strate                                                                                                          |  |

|                          |           | a His Marth | 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - |  |

- > Photoresist is a light sensitive material. It is of 2 types.

- 1) Positive photoresist

- 2) Negative photoresist

- > Positive photoresist is initially insoluble and becomes soluble after exposure to UV light.

- Negative photoresist is initially soluble and becomes insoluble after exposure to UV light.

- Here we use positive photoresist. So, we have to cover some of the areas on the surface and selectively expose the photoresist.

- > The areas becomes soluble, which are exposed to UV rays.

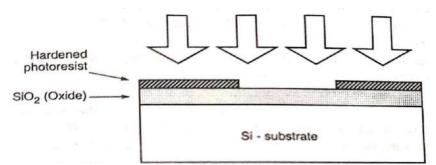

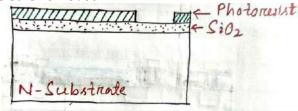

Then the soluble areas can be etched away. Etching is the process of material being removed from the surface.

- > The two major types of etching are wet etching and dry etching.

- The etching process that involves using liquid chemicals to take off the substrate material is called wet etching. Ex- Hydrofluoric Acid, Nitric acid, Acetic acid

- The dry etching is known as plasma etching. Etchant gases are used to remove the substrate material. Ex. Tetra fluoromethane, sulfur hexafluoride, Nitrogen trifluoride, Chlorine gas, Fluorine gas

- Negative photoresists are more sensitive to light, but their photolithographic resolution is not as high as that of the positive photoresists. Therefore, negative photoresists are used less commonly.

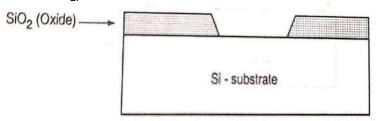

- The silicon dioxide regions which are not covered by hardened photoresist can be etched away either by using a chemical solvent or by using a dry etching process.

> After that the unexposed portions of the photoresist can be removed by a chemical leaving the patterned  $SiO_2$ .

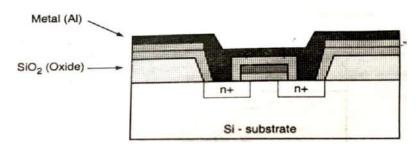

## FABRICATION PROCESS OF NMOS TRANSISTOR-

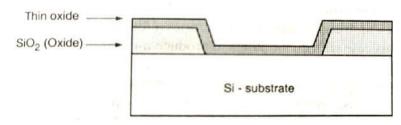

First we take a p type silicon substrate.

> The process starts with the oxidation of the silicon substrate

Then the field oxide is selectively etched to expose the silicon surface.

> Again the surface is covered with a thin oxide layer.

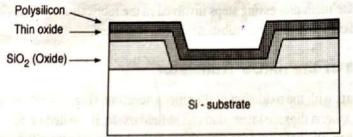

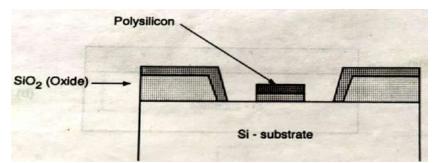

> On top of the thin oxide layer, a layer of polysilicon is deposited.

After deposition, the polysilicon layer is patterned and etched to form gate of the MOSFET.

The thin gate oxide not covered by polysilicon is also etched away, which exposes the silicon surface on which the source and drain junctions are to be formed.

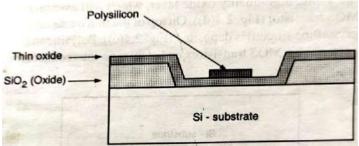

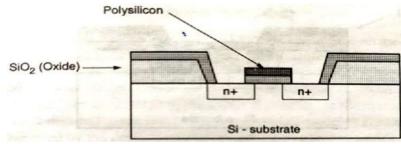

The entire silicon surface is then doped with a high concentration of impurities, ultimately creating two n type regions.

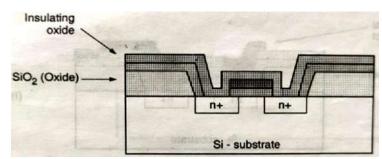

Once the source and drain regions are completed, the entire surface is again covered with an insulating layer of silicon dioxide.

The insulating oxide layer is then patterned in order to provide contact windows for the drain and source.

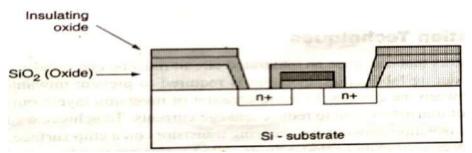

> Then the surface is covered with evaporated aluminum which will form the interconnects.

Finally the metal layer is patterned and etched, completing the interconnection of the MOS transistors on the surface.

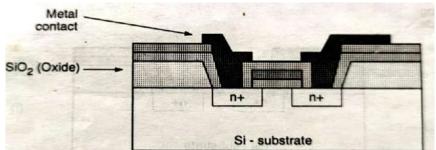

## **CMOS N-WELL FABRICATION PROCESS FLOW-**

- For less power dissipation requirement CMOS technology is used for implementing transistor.

- The ne well technology and p-well technologies are used for fabrication of CMOS. Now let's discuss the steps of CMOS n-well fabrication.

- First we select a substrate as a base for fabrication. So, here we select a p-type substrate.

> Silicon dioxide layer formed by oxidation process on the Si substrate.

| 3.7         |  |  |

|-------------|--|--|

| - # 1       |  |  |

| Bauhatanta  |  |  |

| P-substrate |  |  |

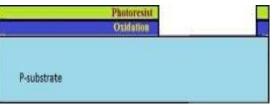

➢ For selective etching the SiO₂ layer is subjected to photolithography process. In this process, the wafer is coated with a uniform film of a photosensitive material known as photoresist.

|             | Photoresist |  |

|-------------|-------------|--|

|             | Oxidation   |  |

|             |             |  |

| P-substrate |             |  |

| Proubstrate |             |  |

> The photoresist layer selectively exposed to UV rays.

| <br> |   | <br> |          |   |   | <br> |

|------|---|------|----------|---|---|------|

| _    | _ | Pho  | toresist | 6 | _ | _    |

|      |   | Ōx   | idation  |   |   |      |

> The soluble photoresist is removed.

> The exposed silicon dioxide region is removed.

> The remaining photoresist layer is removed.

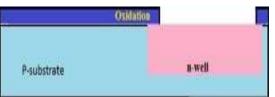

> N well is formed using ion implantation or diffusion.

|             | ation  |

|-------------|--------|

| P-substrate | a-well |

> The remaining silicon dioxide is removed.

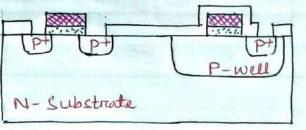

## **CMOS FABRICATION PROCESS BY N-WELL ON P SUBSTRATE-**

> For N well process first we take a P type substrate.

Substrate is oxidized in high temperature.

> Apply photoresist on the surface of the silicon dioxide.

Selectively expose the photoresist to the UV rays.

> The soluble photoresist is removed.

|            | Photoresist |  |

|------------|-------------|--|

|            | Oxidation   |  |

|            |             |  |

|            |             |  |

| P-substrat | e           |  |

|            |             |  |

> The exposed Silicon dioxide region is removed.

> The entire photoresist layer is stripped off.

|             | Oxidátion |  |

|-------------|-----------|--|

|             |           |  |

| P-substrate |           |  |

|             |           |  |

> By using ion implantation or diffusion process N-well is formed.

> The remaining silicon dioxide is removed.

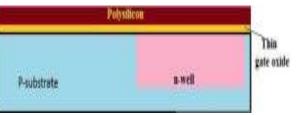

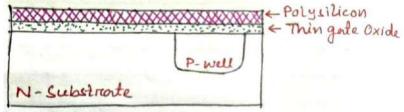

A thin layer of gate oxide is deposited on the surface of the substrate. Then apply the polysilicon on the surface.

> Gate oxide and polysilicon layers are selectively removed.

| P-substrate | n-well |

|-------------|--------|

| P-substrate | 8.05.0 |

> An oxide layer is formed on the surface.

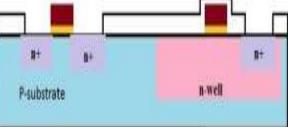

▶ By using the masking process small gaps are made for <u>the purpose</u> of N-diffusion.

> Using diffusion or ion implantation method n type regions are formed.

> The remaining oxide layer is stripped off.

Similar to the above process, the p type regions are formed.

> A thick-field oxide is formed in all regions and then selectively removed.

> Then the surface is covered with evaporated aluminum.

|    |           |    |     |    | - |

|----|-----------|----|-----|----|---|

| p+ | 84        | 8+ | p+  | p+ | Ŧ |

| P  | substrate | 2  | B-W |    | - |

> The excess metal is removed from the surface.

> The terminals of the PMOS and NMOS are made from respective gaps.

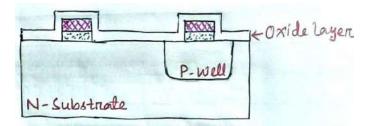

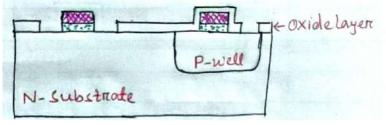

# **CMOS FABRICATION PROCESS BY P-WELL ON N SUBSTRATE-**

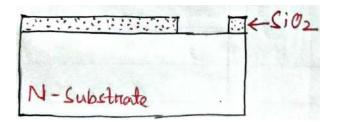

➢ For P well process first we take an N type substrate.

Substrate is oxidized in high temperature.

> Apply photoresist on the surface of the silicon dioxide.

| mmmmm             | - Sioz                |

|-------------------|-----------------------|

| and to distance t | and the second second |

| N-Substrate       | the second second     |

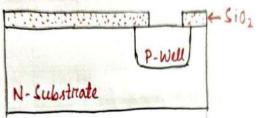

> Selectively expose the photoresist to the UV rays.

> The soluble photoresist is removed.

> The exposed Silicon dioxide region is removed.

|             | Photoresist  |

|-------------|--------------|

| N-Substrate | A CONTRACTOR |

> The entire photoresist layer is stripped off.

> By using ion implantation or diffusion process P-well is formed.

> The remaining silicon dioxide is removed.

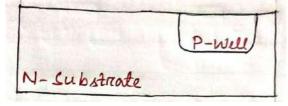

A thin layer of gate oxide is deposited on the surface of the substrate. Then apply the polysilicon on the surface.

> Gate oxide and polysilicon layers are selectively removed.

|             | P-Well |

|-------------|--------|

| N-Substrate |        |

> An oxide layer is formed on the surface.

> By using the masking process small gaps are made for the purpose of P-diffusion.

> Using diffusion or ion implantation method P type regions are formed.

> The remaining oxide layer is stripped off.

Similar to the above process, the n type regions are formed.

> A thick-field oxide is formed in all regions and then selectively removed.

> Then the surface is covered with evaporated aluminum.

> The excess metal is removed from the surface.

> The terminals of the PMOS and NMOS are made from respective gaps.

| INTLET DET  | Interpet |

|-------------|----------|

|             | n-well   |

| N-Substrate |          |

LAYOUT DESIGN RULES-

The physical mask layout of any circuit to be manufactured using a particular process must confirm to set of geometric constraints or rules, which are generally called layout design rules.

The design rules are described in two ways-

1) Micron rules-

Micron rules, in which the layout constraints such as minimum feature sizes and minimum allowable feature separations are stated in terms of absolute dimensions in micrometers.

2) Lambda rules-

Lambda rules specify the layout constraints in terms of a single parameter ( $\lambda$ ) and thus allow linear, proportional scaling of all geometrical constraints.

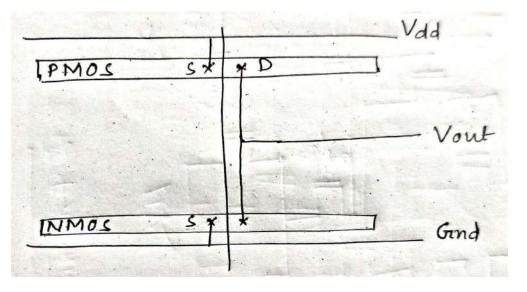

# STICK DIAGRAM OF CMOS INVERTER-

## Stick Diagram-

# <u>UNIT-3</u>

# **MOS INVERTER**

#### **BASIC NMOS INVERTER-**

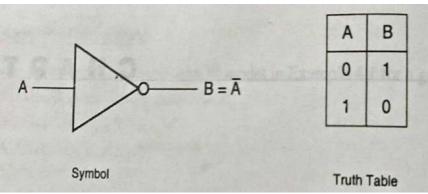

• In ideal inverter circuits, both the input variable A and the output variable B are represented by node voltages.

• Here the Boolean value of '1' means logic 1 can be represented by a high voltage of  $V_{DD}$  and the Boolean value of '0' means logic '0' can be represented by a low voltage of '0'. The voltage  $V_{th}$  is called the inverter threshold voltage.

- For any input voltage between 0 to  $V_{th}$  the output voltage is equal to  $V_{DD}$ . The output switches from  $V_{DD}$  to 0 when the input is equal to  $V_{th}$ .

- For any input voltage between  $V_{th}$  and  $V_{DD}$ , the output voltage is equal to '0'. Thus an input voltage  $0 \le V_{in} < V_{th}$  is interpreted by this ideal inverter as a logic '0'. While an input voltage  $V_{th} < V_{in} \le V_{DD}$  is interpreted as a logic '1'.

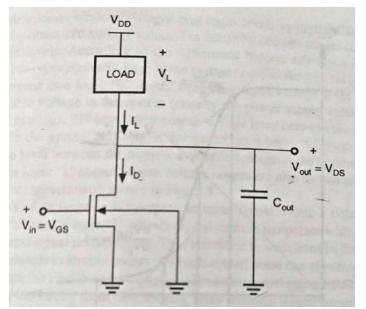

- The input voltage of the inverter circuit is the gate to source voltage of the NMOS transistor. While the output voltage of the circuit is equal to the drain to source voltage.

- The source and the substrate terminals of the NMOS transistor are connected to ground potential. Hence  $V_{SB} = 0$ . The NMOS transistor is used as a driver transistor.

- The drain of NMOS is connected to the output terminal. The load device is represented as a two terminal circuit element with terminal current $I_L$  and terminal voltage  $V_L$ .

- One terminal of the load device is connected to the drain of the NMOS, while the other terminal is connected to  $V_{DD}$ .

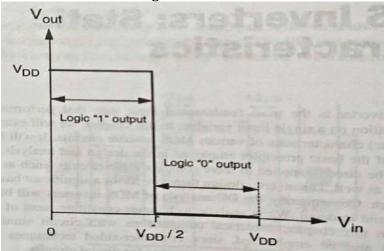

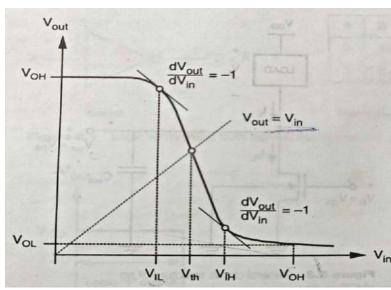

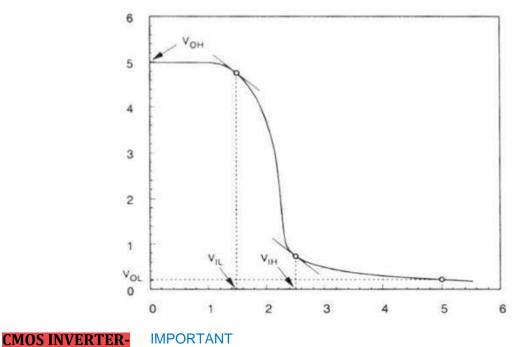

VTC Curve-

- VTC curve, which is a plot of input vs output voltage. The VTC indicates that for low input voltage the circuit output is high and for high input, the output decreases towards 0 volt.

- Applying Kirchhoff's current law, the load current is always equal to the NMOS drain current.

- For very low input voltage levels the output voltage  $V_{out}$  is equal to the high value of  $V_{OH}$ . The driver NMOS transistor is in cut off and hence does not conduct any current. The voltage drop across the load device is very small in magnitude and the output voltage is high.

- As the input voltage *V*<sub>in</sub> increases, the driver transistor starts conducting a drain current and the output voltage starts to decrease. This drop in the output voltage level does not occur abruptly but in an ideal inverter it occur abruptly.

- In this curve two critical voltage points are present, where the slope becomes equal to -1.

$$\frac{dV_{out}}{dV_{in}} = -1$$

- The smaller input voltage at which first slope occur is called the input low voltage  $V_{IL}$  and the larger input voltage at which second slope occur is called the input high voltage  $V_{IH}$ .

- As the input voltage is further increased, the output voltage continues to drop and reaches a value of  $V_{OL}$ , when the input voltage is equal to  $V_{OH}$ . The inverter threshold voltage  $V_{th}$  which is considered as the transition voltage is defined as the point where  $V_{OUT} = V_{in}$ .

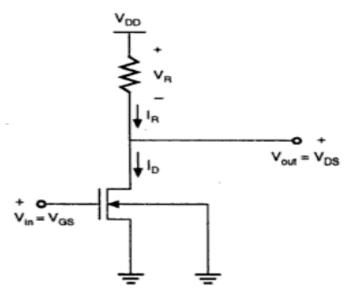

#### **RESISTIVE LOAD INVERTER**- IMPORTANT

Here, enhancement type nMOS acts as the driver transistor. The load consists of a simple linear resistor  $R_{\scriptscriptstyle L}$ . The power supply of the circuit is  $V_{\scriptscriptstyle DD}$  and the drain current  $I_{\scriptscriptstyle D}$  is equal to the load current  $I_{\scriptscriptstyle R}$ .

# **Circuit Operation**

- When the input of the driver transistor is less than threshold voltage, driver transistor is in cut off region and does not conduct any current. So, the voltage drop across the load resistor is zero and output voltage is equal to the V<sub>DD</sub>.

- Here  $I_R = I_D$ .

- So, output voltage V<sub>out</sub> is

$$V_{out} = V_{DD} - I_R R$$

$$V_{out} = V_{DD} - I_D R$$

So, Drain current equation will be

$$I_D = \frac{V_{DD} - V_{out}}{R}$$

- When the input voltage increases further, driver transistor will start conducting the nonzero current and NMOS goes in saturation region.

- if MOSFET is there in saturation region then

$$V_{in} - V_{To} < V_{out}$$

and  $I_D = \frac{K}{2} (V_{GS} - V_{TO})^2$

► If MOSFET is there in linear region then

$$V_{in} - V_{To} > V_{out}$$

and  $I_D = \frac{\kappa}{2} [2(V_{GS} - V_{TO})V_{DS} - V_{DS}^2]$

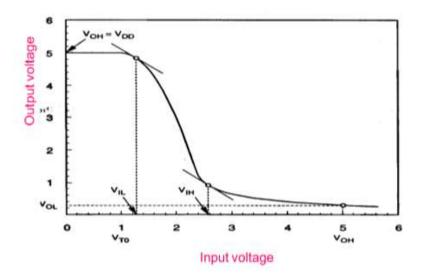

VTC curve-

- Initially when input is at lower voltage, the NMOS is at cut off region, the  $V_{out}$  is equal to  $V_{DD}$  until the NMOS is not turned ON.

- Once the NMOS turned ON, slow decrease in output voltage starts.

# V<sub>OH</sub>-

Output voltage V<sub>out</sub> is

$$V_{out} = V_{DD} - I_D R$$

$$= V_{out} = V_{DD}$$

$$= V_{OH} = V_{DD}$$

V<sub>OL</sub>-

• When  $V_{in} - V_{To} > V_{out}$ , MOSFET is there in linear region, so, drain current will be

$$I_{D} = \frac{\kappa}{2} [2(V_{in} - V_{TO})V_{out} - V_{out}^{2}]$$

• According to kirchoff's law in the drain current is

$$I_D = \frac{V_{DD} - V_{out}}{R}$$

► If we compare these two equations

$$\frac{V_{DD} - V_{Out}}{R} = \frac{K}{2} [2(V_{in} - V_{TO})V_{out} - V_{out}^{2}]$$

$$= > \frac{V_{DD} - V_{OL}}{R} = \frac{K}{2} [2(V_{DD} - V_{TO})V_{OL} - V_{OL}^{2}]$$

=>

$$V_{OL}^2 - 2(V_{DD} - V_{TO} + \frac{1}{KR})V_{OL} + \frac{2}{KR}V_{DD} = 0$$

If we solve the above equation, we get

$$V_{OL} = V_{DD} - V_{TO} + \frac{1}{KR} - \sqrt{(V_{DD} - V_{TO} + \frac{1}{KR})^2 - \frac{2V_{DD}}{KR}}$$

V<sub>IL</sub>-

• When  $V_{in} - V_{To} < V_{out}$  MOSFET is there in saturation region, so drain current will be

$$I_D = \frac{K}{2} (V_{in} - V_{TO})^2$$

• Again compare the equation with circuit drain current equation

$$\frac{V_{DD}-V_{out}}{R} = \frac{K}{2} \left( V_{in} - V_{TO} \right)^2$$

• We have to differentiate it with respect to  $V_{in}$

$$\left(\frac{V_{DD}-V_{out}}{R}\right)\frac{dV_{out}}{dV_{in}} = \left[\frac{K}{2}\left(V_{in}-V_{TO}\right)^{2}\right]\frac{dV_{out}}{dV_{in}}$$

$$= > -\frac{1}{R} \frac{dV_{out}}{dV_{in}} = K\left(V_{in}-V_{TO}\right)$$

$$= > \frac{1}{R} = K(V_{IL}-V_{TO})$$

$$= > V_{IL} = V_{TO} + \frac{1}{KR}$$

$$V_{IH}$$

• When  $V_{in} - V_{To} > V_{out}$  MOSFET is there in linear region, so drain current will be

$$I_{D} = \frac{\kappa}{2} [2(V_{in} - V_{TO})V_{out} - V_{out}^{2}]$$

Compare the equation with circuit drain current equation

$$\frac{V_{DD} - V_{out}}{R} = \frac{K}{2} [2(V_{in} - V_{TO})V_{out} - V_{out}^{2}]$$

• We have to differentiate it with respect to  $V_{in}$

$$\begin{aligned} &-\frac{1}{R} \frac{dV_{out}}{dV_{in}} = \frac{K}{2} \left[ 2(V_{in} - V_{TO}) \frac{dV_{out}}{dV_{in}} + 2V_{out} - 2V_{out} \frac{dV_{out}}{dV_{in}} \right] \\ &= > \frac{1}{R} = \frac{K}{2} \left[ -2(V_{IH} - V_{TO}) + 4V_{out} \right] \\ &= > \frac{1}{KR} = -(V_{IH} - V_{TO}) + 2V_{out} \\ &= > \frac{1}{KR} = -V_{IH} + V_{TO} + 2V_{out} \\ &= > V_{IH} = V_{TO} + 2V_{out} - \frac{1}{KR} \end{aligned}$$

#### **INVERTER WITH N-TYPE MOSFET LOAD-**

The main advantage of using MOSFET as load device is that the silicon area occupied by the transistor is smaller than the area occupied by the resistive load. Here, MOSFET is active load and inverter with active load gives a better performance than the inverter with resistive load.

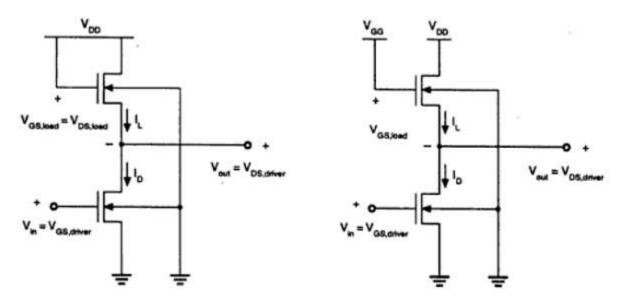

#### **Enhancement load-**

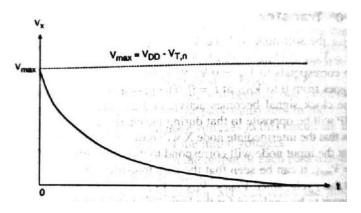

Load transistor can be operated either, in saturation region or in linear region, depending on the bias voltage applied to its gate terminal. The saturated enhancement load inverter is shown in the first figure. It requires a single voltage supply and simple fabrication process and so  $V_{OH}$  is limited to the  $V_{DD}$  –  $V_T$ .

The linear enhancement load inverter is shown in the second figure. It always operates in linear region; so  $V_{OH}$  level is equal to  $V_{DD}$ .

Linear load inverter has higher noise margin compared to the saturated enhancement inverter. But, the disadvantage of linear enhancement inverter is, it requires two separate power supply and both the circuits suffer from high power dissipation. Therefore, enhancement inverters are not used in any large-scale digital applications.

#### **Depletion load NMOS-**

- Drawbacks of the enhancement load inverter can be overcome by using depletion load inverter. Compared to enhancement load inverter, depletion load inverter requires few more fabrication steps for channel implant to adjust the threshold voltage of load.

- The advantages of the depletion load inverter are sharp VTC transition, better noise margin, single power supply and smaller overall layout area.

- The gate and source terminal of load are connected; So, V<sub>GS</sub> = 0. Thus, the threshold voltage of the load is negative. Hence,

$$V_{GS,load} > V_{T,load}$$

Therefore, load device always has a conduction channel regardless of input and output voltage level.

• When the load transistor is in saturation region, the load current is given by

$$I_{D,load} = \frac{K_{n,load}}{2} \left[ -V_{T,load}(V_{out}) \right]$$

• When the load transistor is in linear region, the load current is given by

$$I_{D,load} = \frac{K_{n,load}}{2} \left[ 2 \left| V_{T,load}(V_{out}) \right| (V_{DD} - V_{out}) - (V_{DD} - V_{out})^2 \right]$$

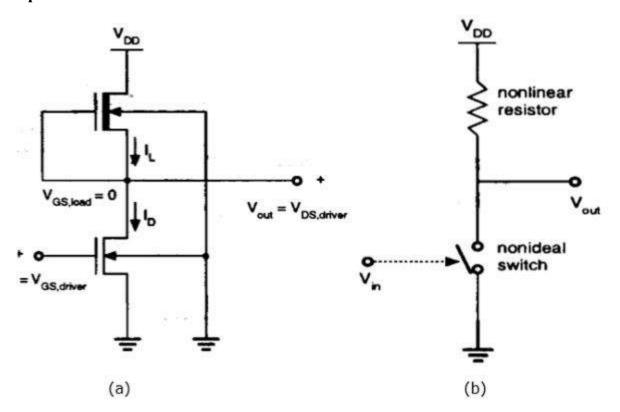

The voltage transfer characteristics of the depletion load inverter is shown in the figure given below –

In CMOS inverter NMOS work as driver and PMOS transistors work as load and always one

transistor is ON, other is OFF.

This configuration is called **complementary MOS (CMOS)**. The input is connected to the gate terminal of both the transistors such that both can be driven directly with input voltages. Substrate of the NMOS is connected to the ground and substrate of the PMOS is connected to the power supply,  $V_{DD}$ .

So  $V_{SB} = 0$  for both the transistors.

$$V_{GS,n} = V_{in}$$

$$V_{DS,n} = V_{OUT}$$

And,

$$V_{GS,n} = V_{in} - V_{DD}$$

$$V_{DS,n} = V_{out} - V_{DD}$$

When the input of nMOS is smaller than the threshold voltage (V<sub>in</sub> < V<sub>TO,n</sub>), the nMOS is cut – off and pMOS is in linear region. So, the drain current of both the transistors is zero.

$$I_{D,n} = I_{D,p} = 0$$

Therefore, the output voltage  $V_{\rm OH}$  is equal to the supply voltage.

$$V_{out} = V_{OH} = V_{DD}$$

When the input voltage is greater than the  $V_{DD}$  +  $V_{TO,p}$ , the pMOS transistor is in the cutoff region and the nMOS is in the linear region, so the drain current of both the transistors is zero.

$I_{D,n} = I_{D,p} = 0$

Therefore, the output voltage  $V_{OL}$  is equal to zero.

$$V_{out} = V_{OL} = 0$$

The nMOS operates in the saturation region if  $V_{in} > V_{TO}$  and if following conditions are satisfied.

$$V_{DS,n} \ge V_{GS,n} - V_{TO,n}$$

$V_{out} \ge V_{in} - V_{TO,n}$

The pMOS operates in the saturation region if  $V_{in} < V_{DD} + V_{TO,p}$  and if following conditions are satisfied.

$$V_{DS,P} \le V_{GS,P} - V_{TO,P}$$

$$V_{out} \ge V_{in} - V_{TO,P}$$

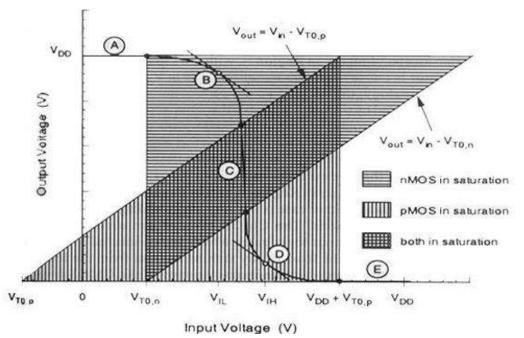

For different value of input voltages, the operating regions are listed below for both transistors.

| Region | V <sub>in</sub>      | Vout                   | nMOS       | pMOS       |

|--------|----------------------|------------------------|------------|------------|

| А      | < V <sub>T0, n</sub> | V <sub>OH</sub>        | Cut – off  | Linear     |

| В      | V <sub>IL</sub>      | High ≈ V <sub>OH</sub> | Saturation | Linear     |

| С      | V <sub>th</sub>      | V <sub>th</sub>        | Saturation | Saturation |

| D | V <sub>IH</sub>          | Low $\approx V_{OL}$ | Linear | Saturation |

|---|--------------------------|----------------------|--------|------------|

| E | $> (V_{DD} + V_{TO, p})$ | V <sub>OL</sub>      | Linear | Cut – off  |

The VTC of CMOS is shown in the figure below -

# **INTERCONNECT EFFECTS-**

#### DELAY TIME DEFINATION - IMPORTANT

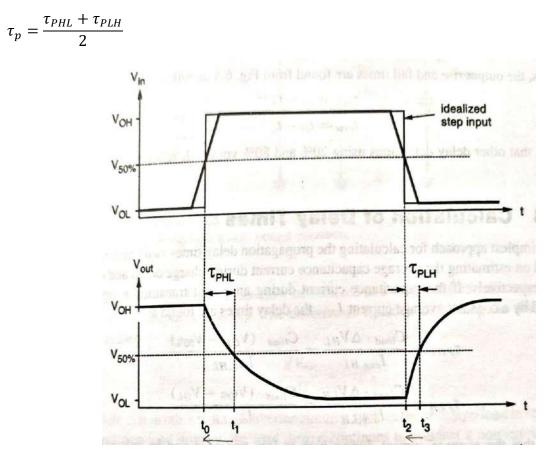

The propagation delay times  $\tau_{PHL}$  and  $\tau_{PLH}$  determine the input to output signal delay during the high to low and low to high transitions of the output, respectively.

Definition-

$\tau_{PHL}$  is the time delay between the  $V_{50\%}$  transition of the rising input voltage and the  $V_{50\%}$  transition of the falling output voltage.

$\tau_{PLH}$  is the time delay between the  $V_{50\%}$  transition of the falling input voltage and the  $V_{50\%}$  transition of the rising output voltage.

$\tau_{PHL}$  becomes the time required for the output voltage to fall from  $V_{OH}$  to the  $V_{50\%}$  level and

$\tau_{PLH}$  becomes the time required for the output voltage to rise from  $V_{OL}$  to the  $V_{50\%}$  level.

$$V_{50\%} = V_{OL} + \frac{1}{2}(V_{OH} - V_{OL})$$

$$= \frac{1}{2} (V_{OL} + V_{OH})$$

$\tau_{PHL} = t_1 - t_0$

$\tau_{PLH} = t_3 - t_2$

Average propagation delay is

## **INVERTER DESIGN WITH DELAY CONSTRAINTS-**

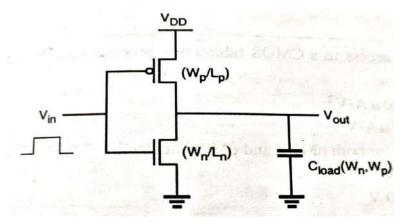

The design of CMOS inverters based on timing specifications is one of the most fundamental issues in digital circuit design which ultimately determine the overall performance of complex systems.

The load capacitance *C*<sub>load</sub> consists of intrinsic components and extrinsic components.

If  $C_{load}$  consists of extrinsic components and if this overall load capacitance can be estimated accurately and independently of the transistor dimensions, then the problem of inverter design can be reduced. Given a required delay value of  $\tau_{PHL}$ , the (W/L) ratio of the NMOS transistor can be found as

$$\frac{W_n}{L_n} = \frac{C_{load}}{\tau_{PHL}\mu_n C_{ox} (V_{DD} - V_{T,n})} \left[ \frac{2V_{T,n}}{V_{DD} - V_{T,n}} + ln \left( \frac{4(V_{DD} - V_{T,n})}{V_{DD}} - 1 \right) \right]$$

Similarly, the (W/L) ratio of the PMOS transistor to satisfy a given target value of  $\tau_{PLH}$  can be calculated as

$$\frac{W_P}{L_P} = \frac{C_{load}}{\tau_{PLH}\mu_P C_{ox}(V_{DD} - |V_{T,P}|)} \left[ \frac{2|V_{T,P}|}{V_{DD} - |V_{T,P}|} + ln\left(\frac{4(V_{DD} - |V_{T,P}|)}{V_{DD}} - 1\right) \right]$$

Assumed that the combined output load capacitance is mainly dominated by its extrinsic components, and hence, that is not very sensitive to device dimensions.

$$C_{load} = C_{gd,n}(W_n) + C_{gd,p}(W_p) + C_{db,n}(W_n) + C_{db,p}(W_p) + C_{int} + C_g$$

= f (W<sub>n</sub>, W<sub>p</sub>)

The fan out capacitance  $C_g$  is also a function of the device dimensions in the next stage gate.

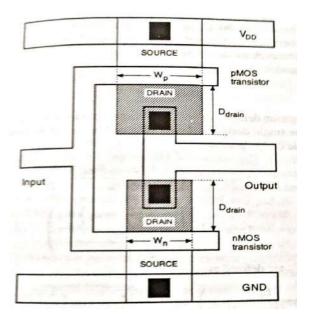

Simplified CMOS inverter mask layout used for delay analysis

Here the diffusion areas of both NMOS and PMOS transistors have a simple rectangular geometry and the drain region length is assumed to be same for both devices. The relatively small gate to drain capacitances  $C_{gd,n}$  and  $C_{gd,p}$  will be neglected. The drain parasitic capacitances can be found as

$$C_{db,n} = W_n D_{drain} C_{j0,n} K_{eq,n} + 2(W_n + D_{drain}) C_{jsw,n} K_{eq,n}$$

$$C_{db,p} = W_p D_{drain} C_{j0,p} K_{eq,p} + 2(W_p + D_{drain}) C_{jsw,p} K_{eq,p}$$

Where  $C_{j0,n}$  and  $C_{j0,p}$  denote the zero bias junction capacitances for n-type and p-type diffusion regions,  $C_{jsw,n}$  and  $C_{jsw,p}$  denote the zero bias sidewall junction capacitances and  $K_{eq,n}$  and  $K_{eq,p}$  denote the voltage equivalence factors. The combined output load capacitance then becomes

$$C_{load} = (W_n C_{j0,n} K_{eq,n} + W_p C_{j0,p} K_{eq,p}) D_{drain} + 2(W_n + D_{drain}) C_{jsw,n} K_{eq,n} + 2(W_p + D_{drain}) C_{jsw,p} K_{eq,p} + C_{int} + C_q$$

Thus the total capacitive load of the inverter can be expressed as

$$C_{load} = \alpha_0 + \alpha_n W_n + \alpha_p W_p$$

Where  $\alpha_0 = 2D_{drain} (C_{jsw,n} K_{eq,n} + C_{jsw,p} K_{eq,p}) + C_{int} + C_g$

$\alpha_n = K_{eq,n} (C_{j0,n} D_{drain} + 2C_{jsw,n})$

$\alpha_p = K_{eq,p} (C_{j0,p} D_{drain} + 2C_{jsw,p})$

# <u>UNIT-4</u>

# STATIC COMBINATIONAL, SEQUENTIAL, DYNAMICS LOGIC CIRCUITS & MEMORIES

# STATIC CMOS LOGIC CIRCUITS-

**Static <u>CMOS</u>** is a <u>logic</u> circuit design technique whereby the output is always strongly driven due to it always being connected to either <u>VCC</u> or <u>GND</u> (except when switching). This design is in contrast to <u>Dynamic CMOS</u> which relies on the temporary storage of signal using various load capacitances.

A static CMOS circuit is composed of two networks:

- pull-up network (PUN) a set of PMOS transistors connected between V<sub>cc</sub> and the output line

- pull-down network (PDN) a set of NMOS transistors connected between GND and the output line

Components designed out pull-up and pull-down networks operate in a mutually exclusive way; in a steady state there is never a direct path between Vcc and GND. Devices that are made up of PUN/PDN are always strongly driven and therefore offers strong immunity from noise. When both the pull-up and pull-down networks are OFF, the result is high impedance. That state is important for memory elements, tristate bus drives, and various other components such as some multiplexers and buffers. When both the pull-up and pull-down networks are ON, the result is a crowbarred level. This result is typically an unwanted condition

## **CMOS NAND2 Gate-**

- The below figure shows a 2-input Complementary MOS NAND gate. It consists of two series NMOS transistors between Y and Ground and two parallel PMOS transistors between Y and VDD.

- If either input A or B is logic 0, at least one of the NMOS transistors will be OFF, breaking the path from Y to Ground. But at least one of the PMOS transistors will be ON, creating a path from Y to VDD.

Two Input NAND Gate

Hence, the output Y will be high. If both inputs are high, both of the nMOS transistors will be ON and both of the pMOS transistors will be OFF. Hence, the output will be logic low. The truth table of the NAND logic gate given in the below table.

| A | В | Pull-Down<br>Network | Pull-up Network | OUTPUT Y |

|---|---|----------------------|-----------------|----------|

| 0 | 0 | OFF                  | ON              | 1        |

| 0 | 1 | OFF                  | ON              | 1        |

| 1 | 0 | OFF                  | ON              | 1        |

| 1 | 1 | ON                   | OFF             | 0        |

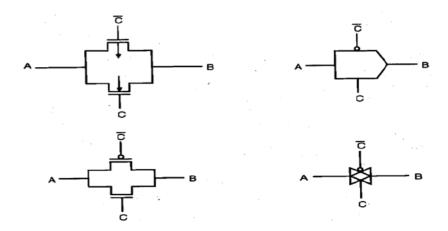

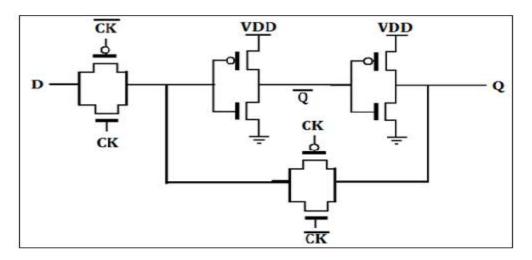

# **CMOS TRANSMISSION GATES-**

CMOS transmission gate consists of one NMOS and one PMOS transistor, connected in parallel. The gate voltages applied to these two transistors are also set to be complementary signals.

Symbols-

The CMOS transmission gate operates as a bidirectional switch between the nodes A and B which is controlled by signal C.

If the control signal C is

- (i) Logic high i.e, equal  $toV_{DD}$ , then both transistors are turned on and provide a low resistance current path between the nodes A and B.

- Logic low then both transistors will be off and the path between the nodes A and B will be an open circuit. This condition is called the high impedance state.

The substrate terminal of the NMOS transistor is connected to ground and the substrate terminal of the PMOS transistor is connected to  $V_{DD}$ .

| С | А | В                    |

|---|---|----------------------|

| 0 | 0 | High impedance State |

| 0 | 1 | High impedance State |

| 1 | 0 | 0                    |

| 1 | 1 | 1                    |

# **COMPLEX LOGIC CIRCUITS-**

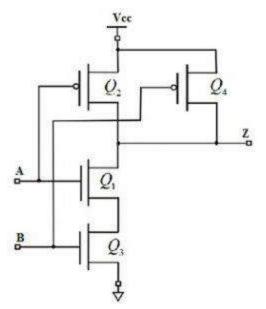

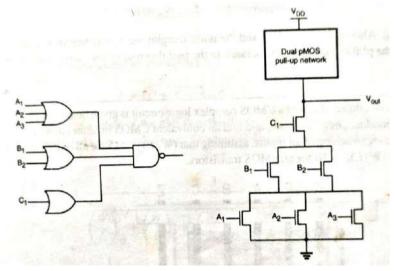

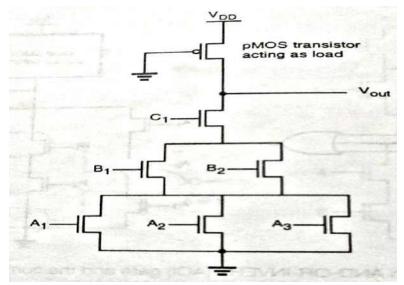

NMOS Depletion Load Complex Logic Gate

To realize complex functions of multiple input variables, the basic circuit structures and design principles developed for NOR and NAND can be extended to complex logic gates. The ability to realize complex logic functions, using a small number of transistors is one of the most attractive features of nMOS and CMOS logic circuits. Consider the following Boolean function as an example.

### Z=(P(S+T)+QR)'

The nMOS depletion-load complex logic gate used to realize this function is shown in figure. In this figure, the left nMOS driver branch of three driver transistors is used to perform the logic function P (S + T), while the right-hand side branch performs the function QR. By connecting the two branches in parallel, and by placing the load transistor between the output node and the supply voltage  $V_{DD}$ , we obtain the given complex function. Each input variable is assigned to only one driver.

Inspection of the circuit topology gives simple design principles of the pull-down network

- OR operations are performed by parallel-connected drivers.

- AND operations are performed by series-connected drivers.

- Inversion is provided by the nature of MOS circuit operation.

# Complex CMOS Logic Gates-

The realization of the n-net, or pull-down network, is based on the same basic design principles examined for nMOS depletion-load complex logic gate. The pMOS pull-up network must be the dual network of the n-net.

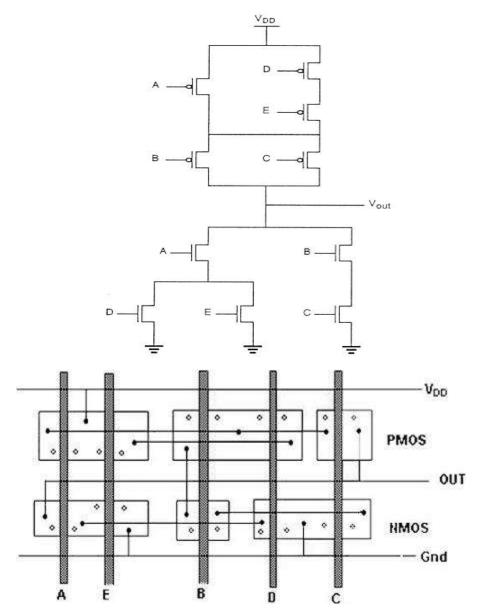

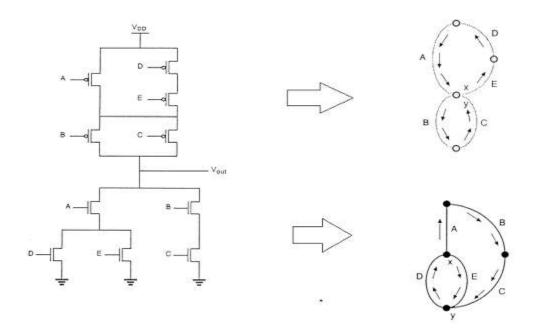

It means all parallel connections in the nMOS network will correspond to a series connection in the pMOS network, and all series connection in the nMOS network correspond to a parallel connection in the pMOS network. The figure shows a simple construction of the dual p-net (pull-up) graph from the n-net (pull-down) graph.

Using an arbitrary ordering of the polysilicon gate columns-

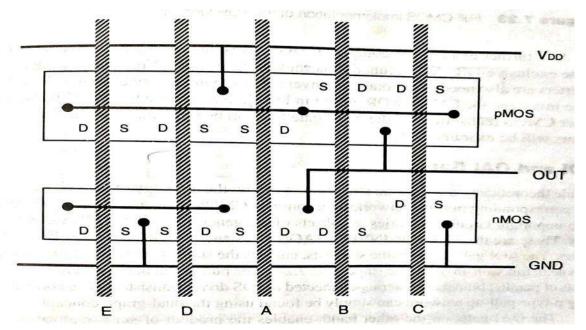

X = (A(D+E)+BC)'

If we can minimize the number of diffusion area breaks both for NMOS and for PMOS transistors, the separation between the polysilicon gate columns can be made smaller, which will reduce the overall horizontal dimension and hence the circuit layout area. The number of diffusion breaks can be minimized by changing the ordering of the polysilicon columns.

A simple method for finding the optimum gate ordering is the Euler-path approach: find a Euler path in the pull down graph and a Euler path in the pull-up graph with identical ordering of input labels i.e, find a common Euler path for both graphs.

# The Euler path is defined as an uninterrupted path that traverses each edge (branch) of the graph exactly once.

There is a common sequence (E-D-A-B-C) in both graphs i.e, a Euler path. The polysilicon gate columns can be arranged according to this sequence.

# AOI and OAI gates-

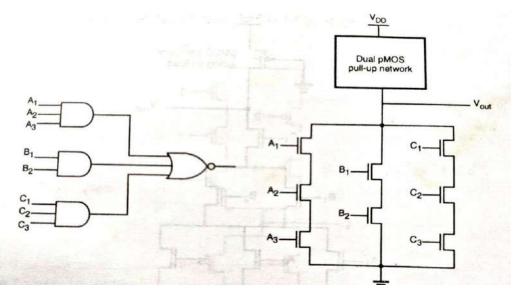

• The AND-OR-INVERT (AOI) gate enables the sum of products realization of a Boolean function in one logic stage. The pull down network of the AOI gate consists of parallel branches of series connected NMOS driver transistors.

• The OAI gate, enables the product-of-sums realization of a Boolean function in one logic stage. The pull down network of the OAI gate consists of series branches of parallel connected NMOS driven transistors.

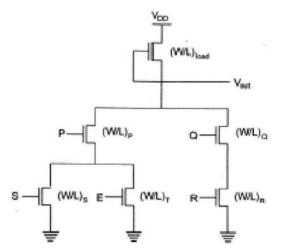

## Pseudo-NMOS gates-

- The large area requirements of complex CMOS gates present a problem in high density designs, since two complementary transistors, one NMOS and one PMOS, are needed for every input.

- One possible approach to reduce the number of transistor is to use a single PMOS transistor, with its gate terminal connected to ground, as the load device.

- With this simple pull up arrangement, the complex gate can be implemented with much fewer transistors.

- The disadvantages of using a pseudo NMOS gate instead of a full CMOS gate is the nonzero static power dissipation, since the always on PMOS load device conducts a steady state current when the output voltage is lower than  $V_{DD}$ .

# CLASSIFICATION OF LOGIC CIRCUITS BASED ON THEIR TEMPORAL BEHAVIOUR-

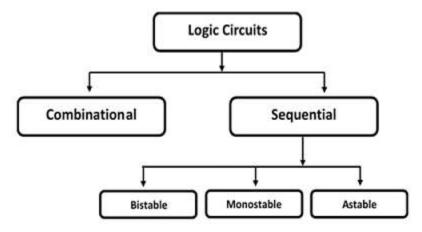

Logic circuits are divided into two categories – (a) Combinational Circuits, and (b) Sequential Circuits.

In Combinational circuits, the output depends only on the condition of the latest inputs.

In Sequential circuits, the output depends not only on the latest inputs, but also on the condition of earlier inputs. Sequential circuits contain memory elements.

Sequential circuits are of three types -

**Bistable** – Bistable circuits have two stable operating points and will be in either of the states. Example – Memory cells, latches, flip-flops and registers.

**Monostable** – Monostable circuits have only one stable operating point and even if they are temporarily perturbed to the opposite state, they will return in time to their stable operating point. Example: Timers, pulse generators.

**Astable** – Astable circuits have no stable operating point and oscillate between several states. Example – Ring oscillator.

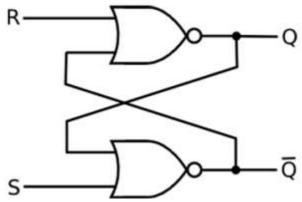

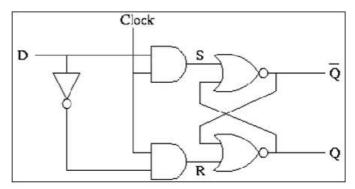

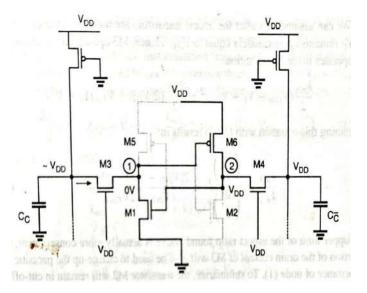

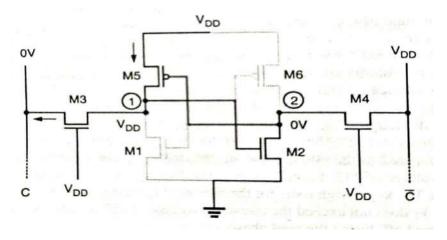

# **SR LATCH CIRCUIT-**

SR Latch based on NOR Gate-

If the set input (S) is equal to logic "1" and the reset input is equal to logic "0." then the output Q will be forced to logic "1". While Q' is forced to logic "0". This means the SR latch will be set, irrespective of its previous state.

Similarly, if S is equal to "0" and R is equal to "1" then the output Q will be forced to "0" while Q' is forced to "1". This means the latch is reset, regardless of its previously held state. Finally, if both of the inputs S and R are equal to logic "1" then both output will be forced to logic "0" which conflicts with the complementarity of Q and Q'.

Therefore, this input combination is not allowed during normal operation. Truth table of NOR based SR Latch is given in table.

| S | R | Q | Q'             | Operation   |

|---|---|---|----------------|-------------|

| 0 | 0 | Q | Q <sup>,</sup> | Hold        |

| 1 | 0 | 1 | 0              | Set         |

| 0 | 1 | 0 | 1              | Reset       |

| 1 | 1 | 0 | 0              | Not allowed |

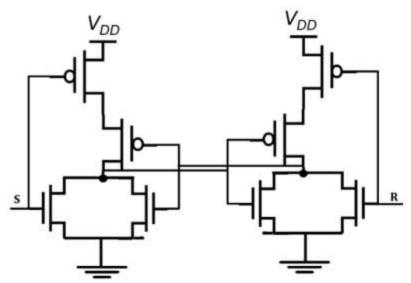

CMOS SR latch based on NOR gate is shown in the figure given below.

If the S is equal to  $V_{\text{\tiny OH}}$  and the R is equal to  $V_{\text{\tiny OL}}$ , both of the parallel-connected transistors M1 and M2 will be ON. The voltage on node Q' will assume a logic-low level of  $V_{\text{\tiny OL}} = 0$ .

At the same time, both M3 and M4 are turned off, which results in a logic-high voltage  $V_{\text{\tiny OH}}$  at node Q. If the R is equal to  $V_{\text{\tiny OH}}$  and the S is equal to  $V_{\text{\tiny OL}}$ , M1 and M2 turned off and M3 and M4 turned on.

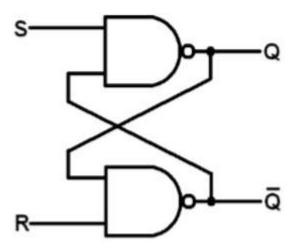

SR Latch based on NAND Gate

Block diagram and gate level schematic of NAND based SR latch is shown in the figure. The small circles at the S and R input terminals represents that the circuit responds to active low input signals. The truth table of NAND based SR latch is given in table

| S | R | Q  | Q′ | OPERATION                                   |

|---|---|----|----|---------------------------------------------|

| 0 | 0 | NC | NC | No change. Latch remained in present state. |

| 1 | 0 | 1  | 0  | Latch SET.                                  |

| 0 | 1 | 0 | 1 | Latch RESET.       |

|---|---|---|---|--------------------|

| 1 | 1 | 0 | 0 | Invalid condition. |

If S goes to 0 (while R = 1), Q goes high, pulling Q' low and the latch enters Set state

$$S = 0$$

then  $Q = 1$  (if  $R = 1$ )

If R goes to 0 (while S = 1), Q goes high, pulling Q'low and the latch is Reset

R = 0 then Q = 1 (if S = 1)

Hold state requires both S and R to be high. If S = R = 0 then output is not allowed, as it would result in an indeterminate state. CMOS SR Latch based on NAND Gate is shown in figure.

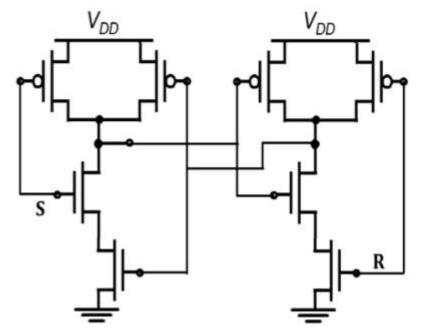

Depletion-load nMOS SR Latch based on NAND Gate is shown in figure. The operation is similar to that of CMOS NAND SR latch. The CMOS circuit implementation has low static power dissipation and high noise margin.

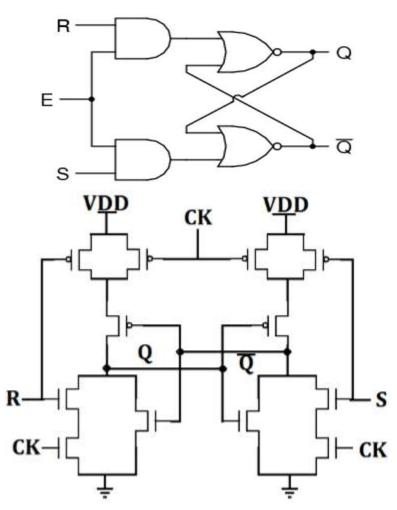

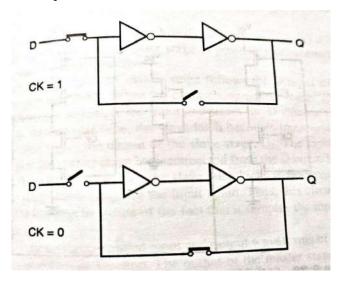

# **CLOCKED SR LATCH-**

For synchronous operations the circuit response can be controlled by adding a gating clock signal to the circuit, so that the outputs will respond to the input levels only during the active period of a clock pulse.

If the clock (CK) is equal to logic "0", the input signals have no influence upon the circuit response. The outputs of the two AND gates will remain at logic "0", which forces SR latch to hold its current state regardless of the S and R input signals.

When the clock input goes to logic "1", the logic levels applied to the S and R inputs are permitted to reach the SR latch and possibly change its state.

With both inputs S and R at logic "1", the occurrence of clock pulse causes both outputs to go momentarily to zero. When the clock pulse is removed i.e, when it becomes "0", the state of the latch is undermined.

CMOS AOI implementation of clocked NOR based SR latch is shown in the figure. If this circuit is implemented with CMOS then it requires 12 transistors.

- When CLK is low, the latch retains its present state.

- When clock is high, the circuit becomes simply a NOR based CMOS latch which will respond to input S and R.

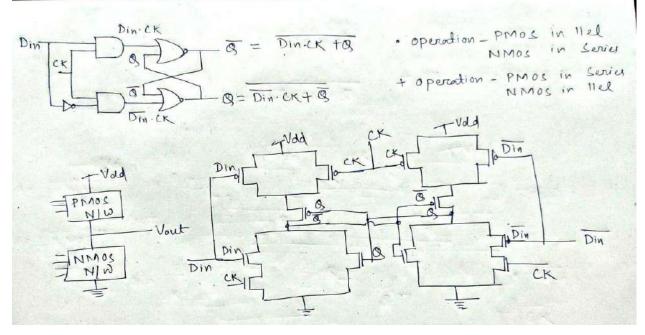

## **CMOS D LATCH-**

- The D latch is simply obtained by modifying the clocked NOR based SR latch circuit. Here, the circuit has a single input D, which is directly connected to the S input of the latch.